嵌入式以太网接口电路的实现

嵌入式以太网不仅可用于工业现场实现现场节点的自动上网功能,而且还可以用于信息家电的以太网接口实现远程控制,具有很好的发展前景。文章介绍基于TMS320LF2407型DSP的嵌入式系统与LAN91C111型自适应10Mb/s/100Mb/s嵌入式以太网控制的接口电路及软硬件实现方法。

本文引用地址:https://www.eepw.com.cn/article/201609/304267.htm1 引言

目前关于嵌入式以太网的设计方案不是很多,其中大多是基于单片机的,缺点是速度慢、成本太高。DSP作为一种特殊的嵌入式微处理器系统,具有嵌入的协处理器和用于快速数据处理的并行数据通道,在嵌入式网络设备中引入DSP技术可以使嵌入式以太网变得更快、更便宜、更容易进行功能扩充。本文介绍了基于TMS320LF2407型的嵌入式系统与LAN91C111型自适应10Mb/s/100Mb/s嵌入式以太网控制芯片的接口电路和实现方法。

2 LAN91C111

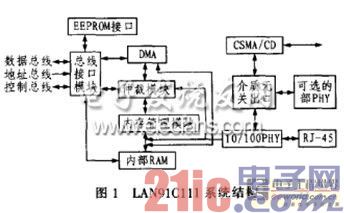

LAN91C111是SMSC公司为嵌入式应用系统推出的第三代快速以太网控制器。LAN91C111的芯片上集成了遵循SMSC/CD协议的MAC(媒体层)和PHY(物理层),符合IEEE802.3/802.U-100Base-Tx/10Base-T规范,其系统结构如图1所示。该以太网控制器的主要功能如下:

·自适应地选传输速率,支持10Mb/s/100Mb/s;

·充分支持全双工交换式以太网;

·支持突发数据传输;

·8k字节的内部存储器用作接收发送的FIFO缓存;

·增强式能量管理功能;

·支持总线8位、16位、32位的CPU访问;

·提前发送和接收。

LAN91C111以太网控制器遵循IEEE颁布的802.3以太网传输协议。其8-32位数据总线接口单元通过控制总线、地址总线和数据总线与外部的CPU相连。外部数据可以8位、16位或32位的方式与LAN91C111进行交换。该电路还集成了EEPROM接口,自举时再通过EEOROM接口输入到芯片中,从而实现自动初始化。总线仲裁器(Arbiter)用来监视以太网总线的数据交流情况,一旦发生阻塞,仲裁器一方面通过总线接口单元与外部CPU联系,另一方面控制内存控制单元(MMU),实现总线数据协调。内存控制单元可控制8kB动态SRAM的存储情况,实现与DMA控制器之间的数据联络。DMA控制器与总线控制器一起控制DMA与以太网协议处理器(EPH)之间的数据交换。以太网协议处理器(EPH)之间的数据交换。以太网协议处理器出来的数量最终经过10Mb/s/100Mb/s的物理层(PHY)直接到达以太网总线。

3 硬件电路组成

出于性价比的考虑,选用DSP控制器作为主CPU。TMS320LF2407是TI公司发布的一款高性价比的,适用于工业控制领域的DSP。该系列具有强大的指令系统、较强的灵活性、高速的数学处理功能及全新的内部结构,可广泛用于通信、计算机、商业、工业、军事等领域。TMS320LF2407是240X系列控制器中功能最强的一款,采用低功耗CMOS技术,具有30MI/s的执行速率,片上还集成了丰富的外围部件(EVM、A/D模块、CAN、SCI、SPI及JTAG)。TMS320LF2407的工作频率较高(40MHz),存贮空间较大(高达32k字的FLASH程序存储器,可扩展外部64k字存储器,64k字I/O寻址空间),非常适合处理复杂的TCP/IP协议。

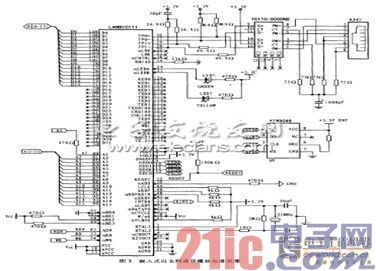

由于LAN91C111是专为嵌入式系统设计的,因此,其外围电路相对比较简单。它和没有DMA传输性能的16位DSP(TMS320LF2407)及TG110-S050N2型电磁耦合变压器构成的嵌入式以太网结构如图2所示。图中,地址总线A1-A15相连。A0没有被LAN91C111使用,悬空;数据总线D0-D15相连,用于16位数据传输。LAN91C111端D16-D32悬空;LAN91C111的片选信号AEN由DSP的外部I/O接口选通信号IS提供。二个元件的读电平RD、写电平WR分别相连。LAN91C111的中断输出信号INTRO送入DSP的外部中断脚XINT1触发中断。嵌入式以太网通信模块的电路原理如图3所示。

嵌入式以太网不仅可用于工业现场实现现场节点的自动上网功能,而且还可以用于信息家电的以太网接口实现远程控制,具有很好的发展前景。文章介绍基于TMS320LF2407型DSP的嵌入式系统与LAN91C111型自适应10Mb/s/100Mb/s嵌入式以太网控制的接口电路及软硬件实现方法。

TX INT:当TX completion FIFO不为空时置1e;

TX EMPTY INT:当TX FIFO为空时置to;

AUTO RELEASE:如果置为1,发送包成功后,packet number不写到TX completion FIFO中,而且它所使用的存储空间被自动释放。

(7)使用“每发送一个包产生一个中断”方案时,AUTO RELEASE=0,该方案的流程如上文所述。使用“每发送一个序列的包产生一个中断”方案时允许TX EMPTY INT和TX INT,AUTORELEASE=1,当发送完FIFO中的最后一个包后,产生TX EMPTY INT中断。若出现严重的发送错误,则产生TX INT中断,同时将发送失败的包的packet number保存到FIFO Ports寄存器,这样DSP就可以知道发送过程停止了。这种方案可以减少DSP的负担,而且存储空间的释放也更迅速。当AUTO RELEASE=1时,DSP不能得到成功发送包的packet number。

4.2.3 接收数据包流程

(1)DSP设置receive control寄存器中的RXEN位,允许接收包。

(2)含有正确地址的包被接收到,从MMU请求存储空间,并分派一个packet number,内部的DMA逻辑产生连续的地址,并将接收到的字写到memory中,如果超界,包被丢弃,存储空间被释放。当检测到包的结束,Status Word被写到接收包的最前面,byte count写到第二个字。如果CRC校验正确,packet number被写到RX FIFO,由于RX FIFO非空时,因此将产生RCV INT中断;如果RCR校验不正确,则存储空间被释放,而且不产生中断。

(3)DSP接收到中断后开始执行中断处理程序,首先读入Interrupt Status寄存器,如果产生接收中断(RCV INT位为1),则可从FIFO ports寄存器得到接收包的packet number,而且可从data register将接收包传送到DSP的内存或外存中。当处理结束,DSP向处理器发送REMOVE AND RELEASE FROM TOP OF RX命令(即设置寄存器MMUCOM为0x0060)以释放使用的存储空间和packet number。

评论