CMOS传感器,3D化发表接二连三

在正在举行的“ISSCC 2016”(2016年1月31日~2月4日,美国旧金山)上,与积层CMOS图像传感器的3D(三维)化相关的发表接连不断。在有9项演讲的“SESSION6 Image Sensors”论坛上,有3项演讲是与CMOS图像传感器的3D化有关的。以前业界就在做3D化尝试,而此次的3项技术除了比原来具有更强的低成本和低功耗意识之外,还在3D化中轻松实现了“模块化”。

本文引用地址:https://www.eepw.com.cn/article/201602/286685.htm

通过模块化手段轻松变更像素数

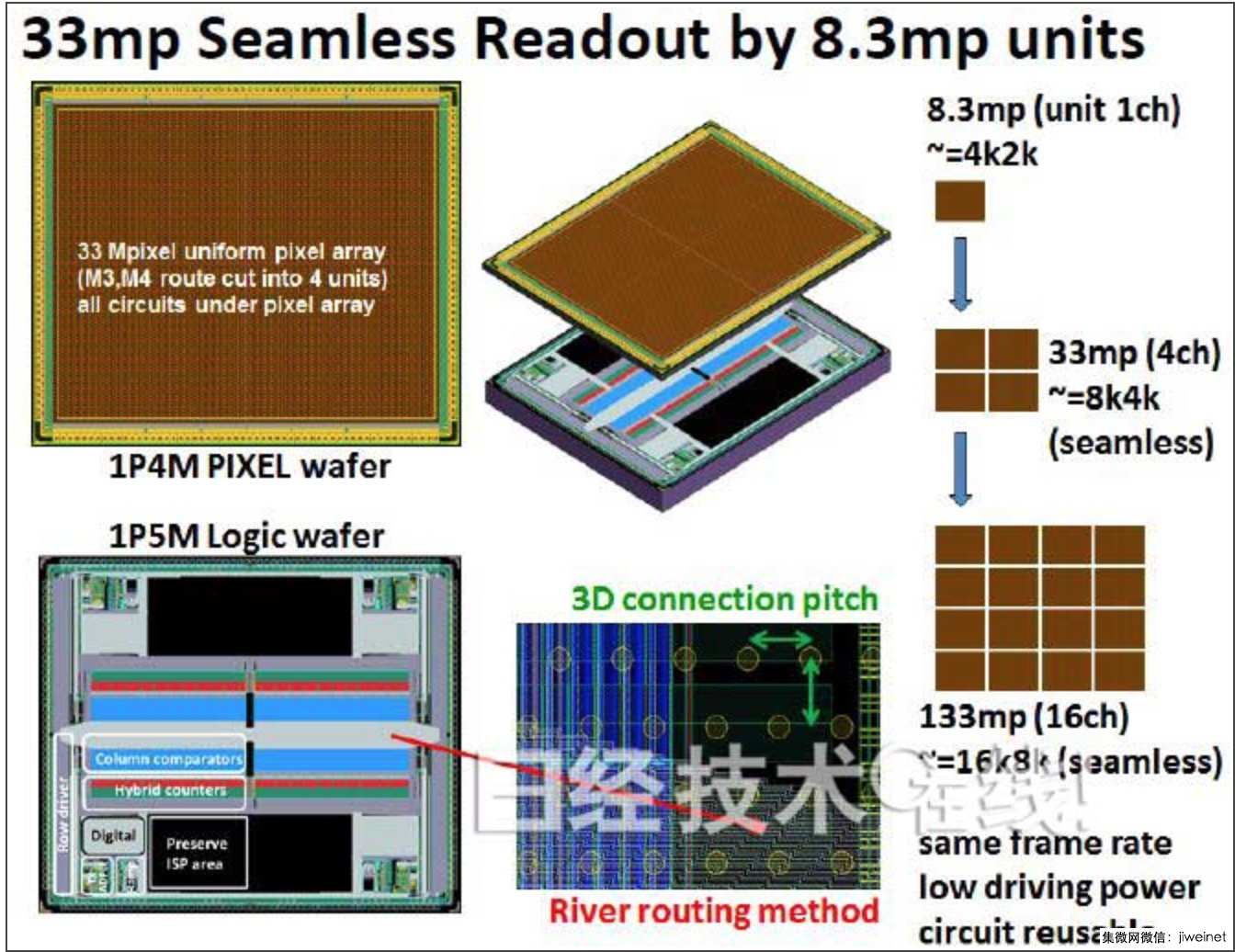

出处:TSMC(2016 IEEE International Solid-State Circuits Conference, 6.8: A 1.5V 33Mpixel 3D-Stacked CMOS Image Sensor with Negative Substrate Bias) (点击放大)

在此次会议上,台积电以“A 1.5V 33Mpixel 3D-Stacked CMOS Image Sensor with Negative Substrate Bias”(Paper6.8)为题发表演讲(见图)。具体内容为:在积层CMOS图像传感器芯片和图像处理电路芯片时,需要应对两者之间的电压差问题,图像处理电路的电压会随着微细化降低至1V左右,而图像传感器则需要2V左右的电压,因此该公司尝试向图像传感器芯片的基板施加负偏压。

该公司在发表中强调了相关模块化技术,该技术通过将约830万像素的4K图像传感器像瓷砖一样组合成一个模块,无需做大的设计变更即可增加像素数。这是凭借将图像处理电路重叠于图像传感器芯片而非二维配置的构成实现的。另外,该公司还使图像处理电路芯片具有了以用于访问各像素的布线为对象的再布线层作用,并在这方面实施了可收放于图像传感器芯片尺寸内的改进。

在积层时,通过使用背面照射(BSI)型CMOS传感器,将图像传感器芯片的布线层一侧与图像处理电路芯片的布线层一侧相向粘合在了一起。其中并未使用成本高的TSV(硅贯通电极),通过粘合实现了电气性接合及绝缘。台积电预计图像传感器用途市场将会进一步扩大,因此借此次学会的机会向潜在客户宣传该公司拥有可满足多种应用需求的基础技术。

通过改进读取电路也可为低功率化做出贡献

东芝在此次会议上以“A 1.2e- Temporal Noise 3D-Stacked CMOS Image Sensor with Comparator-Based Multiple-Sampling PGA”(Paper6.7)为题发表演讲。设想以智能手机为应用对象。该技术分别开发图像传感器芯片和图像处理电路芯片后实施积层,可由此缩短开发期。特点是读取电路采用了低功耗的新式放大电路及A-D转换器。由于东芝正处于发展方向颇为微妙的时期,因此该公司并未在演讲中明确相关技术的业务运作问题。

另外,在此次会议上,NHK放送技术研究所、Brookman Technology、台积电及静冈大学还以“A 1.1μm 33Mpixel 240fps 3D-Stacked CMOS Image Sensor with 3-Stage Cyclic-Based Analog-to-Digital Converters”(Paper6.9)为题发表演讲。内容涉及以NHK等推进实用化的8K电视内容用摄像机,介绍了如何使该摄像机配备的图像传感器实现小型低功耗化的技术。与台积电发表的技术一样,并未使用TSV,而是采用了将BSI型图像传感器与图像处理电路芯片粘合在一起的技术。

该技术将1.1μm间距的像素构成的信号以4×4像素为单位接入下层的图像处理电路芯片的总布线。读取电路的A-D转换器改为3级构成,以高速传输为前提采用适于低功耗化的A-D转换方式。具体而言,1~2级为循环型,3级为逐次逼近型。顺便提一句,相关发表指出,通过在3D化、布线及A-D转换电路方面下工夫,能够实现240帧/秒的8K摄像,不过此次为了用于在学会上发表,拿出的是最优异的数据。NHK技术研究所表示,目前尚未打算依据此次的标准来推进8K电视内容用摄像机的实用化。

在此次会议上,松下发表了3项演讲。其中2项与有机薄膜型图像传感器有关。

评论