NAND FLASH在储存测试系统中的应用

K9K8GOSUOM地址是通过复用8个I/O口送入芯片的。这样的设计显著减少了芯片的管脚数目,并为系统升级带来了方便。在CE和WP为低时,把WE置低可以把K9K8G08UOM的命令、地址和数据通过I/O口写进去。数据在WE的上升沿写入芯片。命令锁存使能(CLE)和地址使能锁存(ALE)用来区分I/O口的数据是命令还是地址。K9K8G08UOM有1G字节地址空间,需要30位的地址,所以字节的地址需要五个周期依次送入:行低地址、行高地址、列低地址、列中地址、列高地址。页的读操作和编程操作都需要同样的五个地址周期紧跟在相应的命令输入之后。然而,在块的擦除操作中,只要有三个地址周期。不同的操作通过往命令寄存器写不同的命令来区分。本文引用地址:http://www.eepw.com.cn/article/194960.htm

1.2 K9K8G08UOM控制器技术

本系统中采用FPGA作为K9K8G08UOM存储器的控制器,可以在极少的软件操作下独立完成K9K8G08UOM的各种操作,从而降低系统对FLASH存储器的额外支出,提高读写速度。FPGA的控制逻辑时序是通过硬件语言VHDL开发的,VHDL语言以其快捷、独立、可读性等优点很好的完成FLASH基本操作的时序控制。下面是以VHDL语言以状态机的形式开发的部分读操作程序。

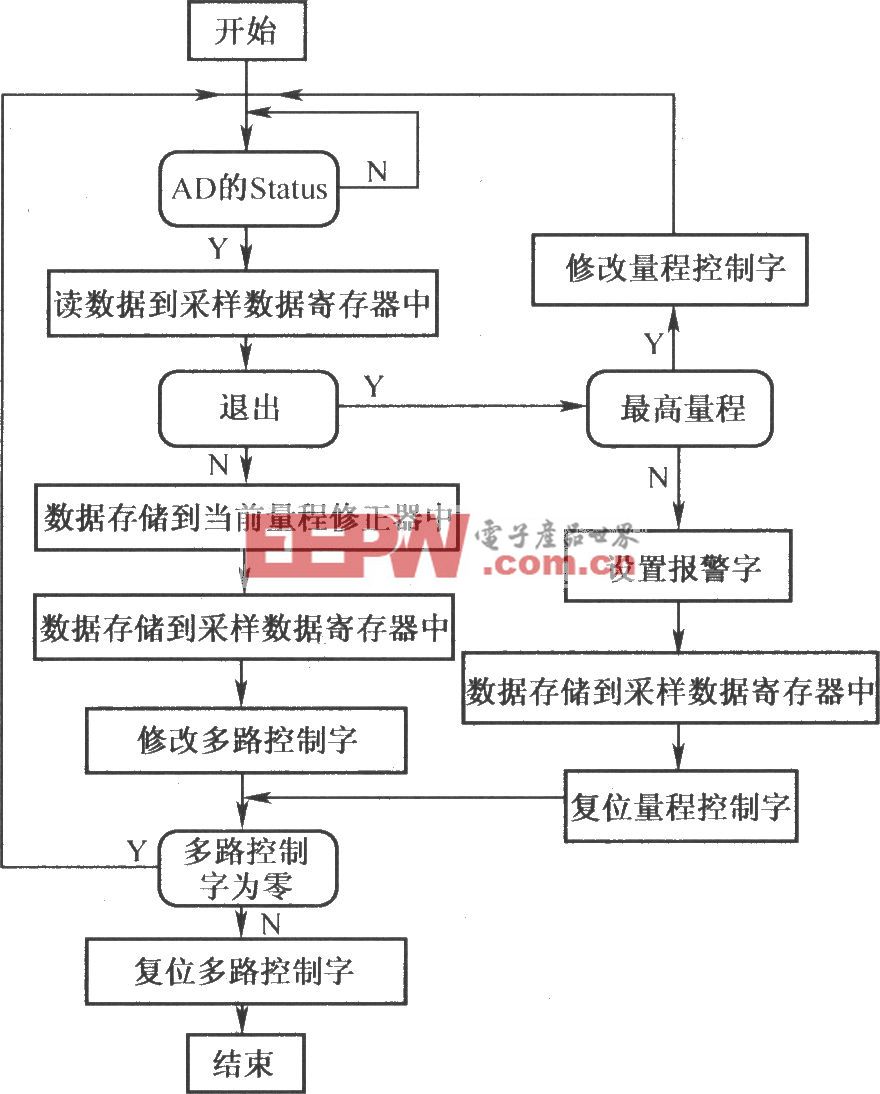

K9K8G08UOM储存器的基本操作由三种类型:读操作、页编程操作、擦除操作,其流程图如图2所示。

进行读操作时,首先通过FPGA的端口置低K9K8G08UJOM的片选信号/CS,然后置高CLE命令脚,并发送read1(0x00)命令,WE的上升沿发送,命令发送完毕后,置低CLE。在发送地址之前,置高ALE,在每一个WE上升沿依次写入5个地址周期,之后置低ALE,完成地址的选定。接着发送read2(0x30h),开始读取地址单元的数据。

数据页编程操作和读取操作流程类似。操作都是以页为单位进行的。当R/Bur信号为低时,说明正在对FALSH进行写入操作,当为高时,说明页编程操作结束。

擦除操作是以块为单位进行的,即一次擦除块内的64页,在发送地址时只需要3个地址周期。

评论