门电路延迟时间的Multisim仿真测试方案

摘 要:介绍了用Multisim 仿真软件测试门电路延迟时间的方法,提出了三种测试方案,即将奇数个门首尾相接构成环形振荡电路,用虚拟示波器测试所产生振荡信号的周期,计算门的传输延迟时间;奇数个门首尾相接构成环形振荡电路,用虚拟示波器测试其中一个门的输入信号、输出信号波形及延迟时间;在一个门的输入端加入矩形脉冲信号,测试一个门的输入信号、输出信号波形及延迟时间。所述方法的创新点是,解决了受示波器上限频率限制实际硬件测试效果不明显的问题,并给出Multisim 软件将门的初始输出状态设置为0 时,使测试电路不能正常工作的解决方法。

本文引用地址:https://www.eepw.com.cn/article/191321.htm0 引 言

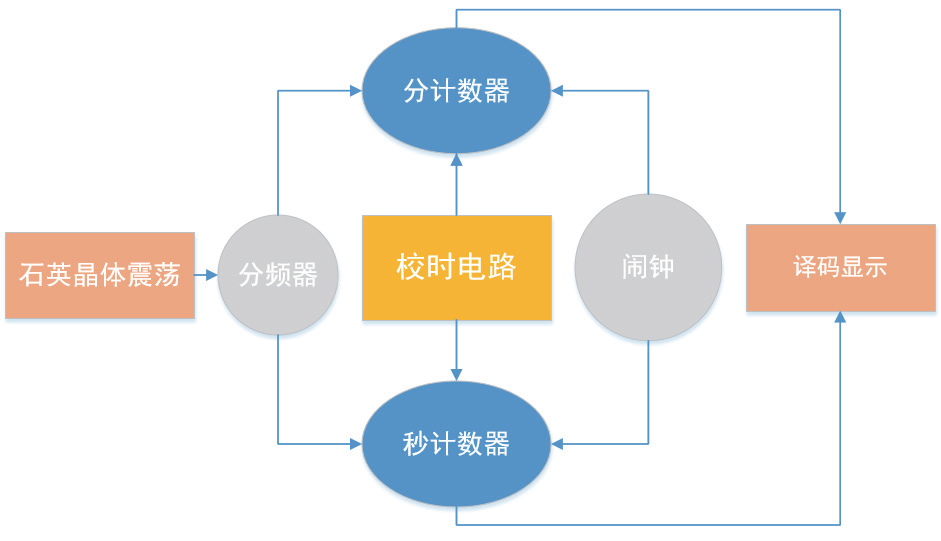

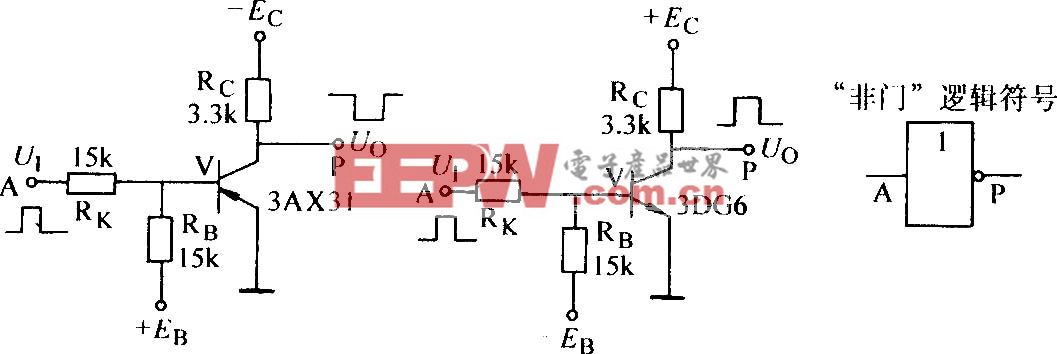

门电路的传输延迟时间tpd 是表示工作速度的指标,实验室硬件测量的一般方法是,将N 个门( N为奇数) 首尾相接构成振荡周期为T = 2N tpd的环形振荡电路,用示波器通过显示的波形测量出振荡周期T后,再计算出传输延迟时间tpd。

由于门的传输延迟时间tpd 很短,测量时受示波器上限频率限制,测量效果较差,而用Mult isim 软件仿真测试,可获得理想的实验效果。

以下分析用Mult isim 2001版本,所得结论也适于其他版本。

1. 1 测试方案1

将奇数个门首尾相接构成环形振荡电路,用虚拟示波器测试所产生振荡信号的周期,计算门的传输延迟时间。

设所用门的个数为N ,振荡信号的周期为T ,则传输延迟时间为:

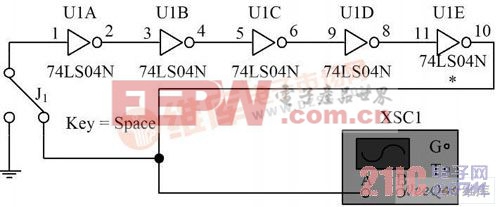

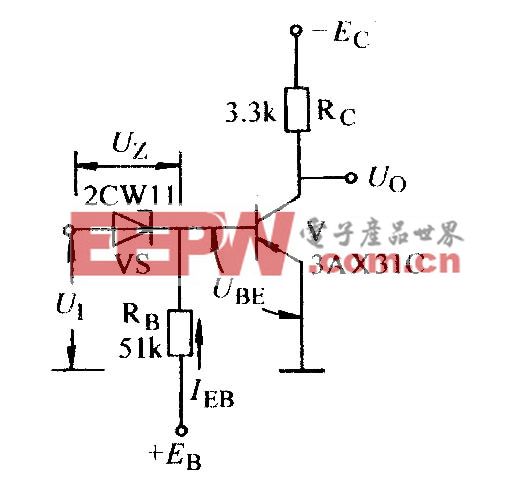

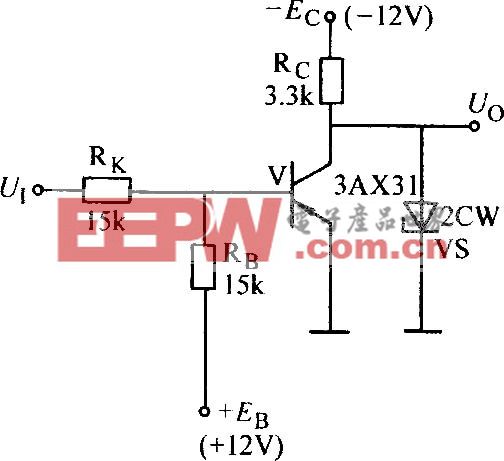

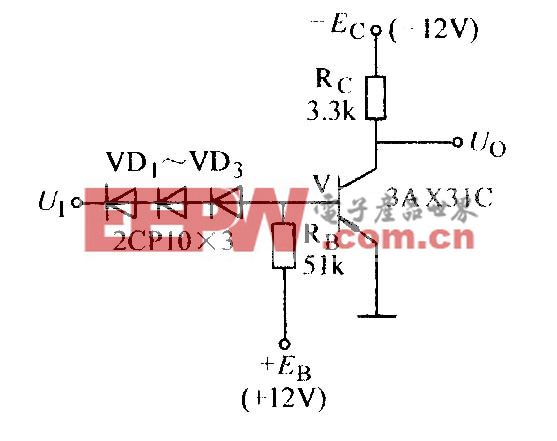

以反相器74LS04N 作为仿真实验器件,构建仿真实验电路如图1 所示。

图1 测试方案1 的仿真实验电路

由于Mult isim 软件将每个门的初始输出状态设置为0,直接用奇数个门首尾相接构成环形振荡电路进行仿真时,出现 nable to determine the simulatiONtimeSTep automatically 的提示,无法同步仿真模拟。

解决的方法是在左边第一个门U1A 的输入端接入转换开关J1 ,仿真时先将开关J1 置于接地状态,电路对输入的0 信号进行处理后便脱离设置的初始输出状态,再将转换开关J1 置于接输出端构成环形振荡电路。

仿真前,可对74LS04N 的上升延迟时间及下降延迟时间进行设置,如设置r ise delay= 10 ns,fall delay=10 ns。

脉冲点火器相关文章:脉冲点火器原理

评论