一种基于FPGA 的嵌入式块SRAM 的设计

摘 要:文章中提出了一种应用于FPGA 的嵌入式可配置双端口的块存储器。该存储器包括与其他电路的布线接口、可配置逻辑、可配置译码、高速读写电路。在编程状态下,可对所有存储单元进行清零,且编程后为两端口独立的双端存储器。当与FPGA 其他逻辑块编程连接时,能实现FIFO 等功能。基于2.5V 电源电压、chart 0.22 μm CMOS 单多晶五铝工艺设计生产,流片结果表明满足最高工作频率200MHz,可实现不同位数存储器功能。

本文引用地址:https://www.eepw.com.cn/article/191314.htm1 引言

对于逻辑芯片的嵌入存储器来说,嵌入式SRAM 是最常用的一种,其典型的应用包括片上缓冲器、高速缓冲存储器、寄存器堆等。除非用到某些特殊的结构,标准的六管单元(6T)SRAM 对于逻辑工艺有着很好的兼容性。对于小于2Mb 存储器的应用,嵌入式SRAM 可能有更好的成本效率并通常首先考虑。

Xilinx 公司SRAM型FPGA 主要由配置存储器、布线资源、可编程I/O、可编程逻辑单元CLB、块存储器BRAM 和数字时钟管理模块组成。它包含了分布式RAM,位于CLB中。每个CLB包含了16 × 1bit的SRAM结构。BRAM的加入既增加了RAM的容量,也可构成大型LUT,更完善了CLB 的功能。

2 BRAM块划分

现代数字系统对存储器容量的存储速率要求越来越高,读访问时间就是一个重要参数,它是从地址信号的出现到存储在该地址上的数据在输出端出现的时间延迟。提高BRAM 读取速度的一个有效办法是减小位线和字线上的总负载电容,这可以通过减少连接在同一字线和位线上的存储单元数目来实现,即采用存储阵列分块技术。本电路采用设计多个BRAM的方法,每个BRAM都有自己的译码电路、敏感放大器和数据通道,各个BRAM 独立工作,每个BRAM 的读取时间得到了大大提高。

3 BRAM块设计

3.1 BRAM与布线资源接口

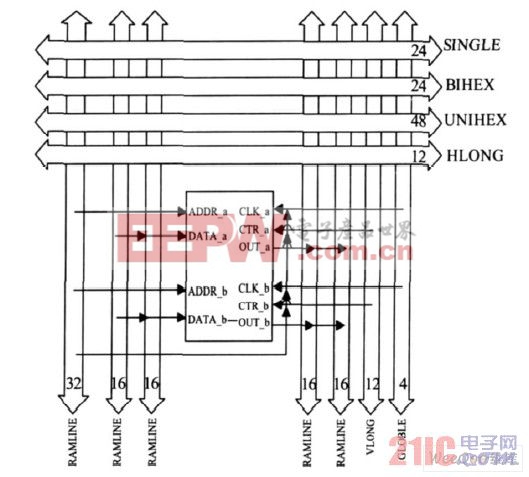

FPGA 中每个BRAM块都嵌在内部连线结构中,与BRAM 直接相连的有RAMLINE、VLONG 和GLOBAL。左边32根RAMLINE提供BRAM的地址输入,也可以提供控制信号(CLK、WE、ENA、RST)的输入。左边两组16 根RAMLINE 一起布线提供BRAM双端口的数据输入,右边两组RAMLINE提供BRAM双端口数据输出通道。4 根GLOBLE全局时钟线优化用作时钟输入,提供较短的延迟和最小的失真。VLONG也被专门用作BRAM中WE、ENA、RST的控制输入。RAMLINE 为BRAM专有布线,如从水平方向的SINGLE、UNIHEX、BIHEX通过可编程开关矩阵PSM 把信号输送到RAMLINE 上,进而送到BRAM 用作地址、数据。而BRAM 的输出也通过RAMLINE最终送到HLONG上。

图1 BRAM周围布线

相邻BRAM 的RAMLINE 也可通过三态门连到下一级的RAMLINE,于是整列中的BRAM 可共享RAMLINE 上的数据。每个BRAM与FPGA其他电路的相连主要通过水平方向的4 组主要互连线完成。

3.2 BRAM内部设计

BRAM为真正的双端口RAM,两个端口完全独立,每个端口可以配置为读写端口,并可以把BRAM配置成特定的数据宽度。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论