基于FPGA的QDPSK调制器的设计与实现

摘要:介绍了QDPSK信号的优点,并分析了其实现原理,提出一种QDPSK高性能数字调制器的FPGA实现方案。采用自顶向下的设计思想,将系统分成串/并变换器、差分编码器、逻辑选相电路、四相载波发生器等4大模块,用原理图输入、VHDL语言设计和调用PLL核相结合的多种设计方法,分别实现了各模块的具体设计,并给出了其在QuartusⅡ环境下的仿真结果。结果表明,基于PLL的QDPSK调制器,设计简单,便于修改和调试,性能稳定。

关键词:QDPSK;串/并变换;数字调制器;FPGA

FPGA器件(Field Programmable Gate Array)是八十年代中期出现的一种新概念。利用FPGA技术设计的产品具有重量轻、体积小、速度快、保密程度高、功耗低等特点,极大地提高了产品的性价比和竞争力,大大缩短了设计周期,减少了设计费用,降低了设计风险。

数字调制信号又称为键控信号,调制过程可用键控的方法由基带信号对载频信号的振幅、频率及相位进行调制。这种调制的最基本方法有3种:振幅健控(ASK)、频移键控(FSK)、相移键控(PSK)。根据所处理的基带信号的进制不同,它们可分为二进制和多进制调制(M进制)。多进制数字调制与二进制相比,其频谱利用率更高。其中QPSK(即4PSK)是MPSK(多进制相移键控)中应用较广泛的一种调制方式,该方式广泛应用于卫星通信、电缆调制解调、视频会议系统、蜂窝电话和其他数字通信领域。然而QPSK信号在解调的时候易产生相位模糊问题,即可能会产生0、π/2、π、3π/2 4种相位模糊。解决的方法就是采用四进制差分相位键控(QDPSK),对于相对移相,基带信号是由相邻两码元相位的变化来表示,它与载波相位无直接关系,即使采用同步解调也不存在相位模糊问题,因此在实际设备中相对移相得到了广泛运用。本文研究了基于FPGA的QDPSK调制电路的实现方法,重点阐述了串/并变换、差分编码、四相载波发生器等电路的原理与实现方法,并给出了其在QuartusⅡ环境下的仿真结果。

1 QDPSK调制原理

1.1 四相绝对移相键控(QDPSK)

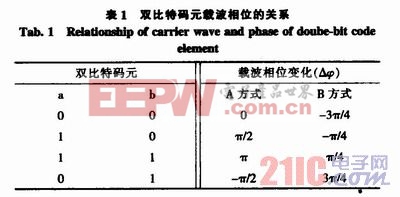

相对调相(相对移相),即DPSK(Differential Phase Shift Keying),也称为差分调相,这种方式用载波相位的相对变化来传送数字信号,即利用前后码之间载波相位的变化表示数字基带信号。在QDPSK信号中,若以前一双比特码元相位作为参考,并令△φ为当前双比特码元的相位差,则可得到双比特码元与载波相位变化关系如表1所示,从表中可以看出,A方式中,载波相位互差π/2,实现比较容易,因此采用A方式。

1.2 QDPSK的调制方法

QDPSK的产生方法可采用调相法和相位选择法。图1为相位选择法产生QDPSK的原理框图。在图1中,四相载波发生器分别送出调相需的4种频率相同、相位互差π/2的载波,输入二进制数字基带信号经串/并变换为四进制数字基带信号,经差分编码变为四进制差分码,逻辑选相电路根据差分编码后的双比特码cd,每隔时间间隔T选择输出其中一种相位的载波。虚线内的信号均为数字信号,可直接利用FPGA来实现ODPSK调制。

评论