基于Wishbone和端点IP的PCIE接口设计

摘要:介绍了FPGA内嵌的PCI Express硬核端点模块和Wishbone片上总线规范。应用VHDL语言,编程实现了Wishbone总线的主从端口,以及TLP包的编码和解码功能。在FPGA上运行程序并使用Chipscope测试时序波形,验证了接口数据传输的稳定性和正确性。

关键词:PCI Express总线;FPGA;PCIE端点模块;Wishbone

0 引言

当前,基于FPGA实现PCI Express接口有两种方案,一是采用第三方PHY接口器件和FPGA实现;二是采用集成GTP的FPGA来实现。集成GTP的FPGA实现PCI Express接口在链路效率、兼容性测试及资源可用性等方面有其独特的优势。随着技术的发展和对传输数据速率和灵活性要求的提高,将更加趋于利用高性能FPGA(即集成GTP的FPGA)来实现PCIExpress接口功能。但是,要在FPGA上实现PCI Express通信桥接,还需要用户根据PCI Express协议构建自己的软IP或者向第三方或FPGA供应商购买IP核。构建IP核的难题在于其难度较大且开发周期较长;向第三方或FPGA供应商购买的IP,存在专利费用问题。对于一些验证性开发,其重点一般在于应用功能的实现,而希望公共模块(如PCI Express接口)的开发在满足性能的前提下,尽量少花时间和费用,从而缩短开发周期和成本。因此,利用已有可获取资源,实现PCI Express接口成为这类开发中的首选。

Xilinx的V5/V6系列FPGA芯片中已集成了硬核端点的PCI Express模块,提供了PCI Express接口的底层配置,相当于提供了一个专用协议与PCI Express之间的桥梁。在PCI Express硬核端点上集成片上总线,实现PCI Express与应用模块互联,将能更快地实现PCI Express接口的开发。

目前比较常见的片上总线规范有IBM公司的CoreConnect,ARM公司的AMBA和Silicore Corp公司的Wishbone。CoreConnect和AMBA规范复杂,在设计中需要建立连接桥以连接不同IP核。相对于其他两种接口规范,Wishbone接口规范具有简单、高效、易于实现等特点,而且完全免费。因此,本文采用Wishbone总线规范实现PCI Exprpess接口。

1 Wishbone基本原理、Xilinx集成端点IP及TLP包结构

1.1 Wishhone的基本原理

Wishbone最先是由Silicore公司提出的,现在己被移交给OpenCores组织维护。其开放性、简单性和灵活性受到广大设计者的青睐,现在己有不少的用户群体,特别是一些免费的IP核,采用Wishbone标准。除了具备地址/数据总线宽度可变、互联结构可变及仲裁机制灵活等片上总线的共同特点外,Wishhone还包括以下特征:

(1)支持点到点、共享总线、十字交叉和基于交换结构的互联;

(2)支持常用的总线数据传输协议,如单字节读写周期、块传输周期、控制操作及其他的总线事务等;

(3)主/从结构,支持多控制器和64位地址空间,从端部分地址解码;握手协议使得每个核都可以控制数据的传输速度;

(4)用户自定义标记(TAG),确定数据传输类型、中断向量等;

(5)接口简单、紧凑,总线实现的逻辑单元少。

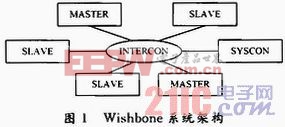

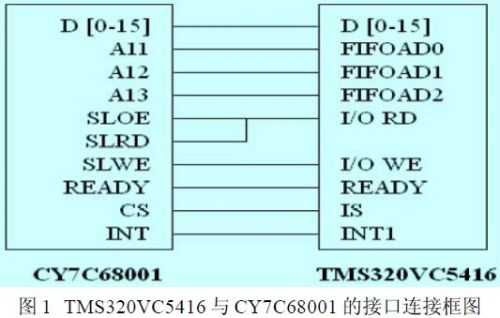

Wishhone采用主端(Master)和从端(Slave)的架构。主端模块发出数据传送请求,然后通过一个接口网络和从端进行数据交换,其系统结构如图1所示。这个接口网络称之为INTERCON,各终端之间访问通过INTERCON,INTERCON内部可根据访问情况采用不同的互连方式,Wishbone将它称为可变互联网络。可变互联网络的连接形式有点对点、数据流、共享总线和交叉总线等。

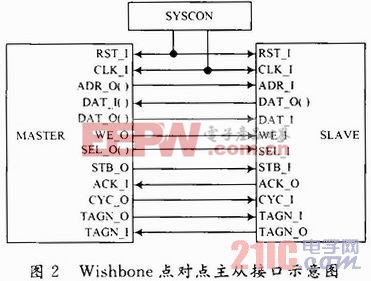

Wishbone可变的互连方式允许系统设计工程师可以采用不同的IP核互连方式,以满足不同场合的要求。根据需要,本设计采用点对点的总线互连方式。图2给出了点对点的MASTER/SLAVE主从接口图。其中SYSCON为产生时钟和复位信号,TAGN为用户自定义信号。

评论