基于Wishbone和端点IP的PCIE接口设计

在每个头中含有类型及格式两个字段,它们定义头剩余部分的格式,用来指定事务的类型、头的大小、数据有效载荷是否存在等。事务(在PCI Express请求者和完成者之间进行的操作)包括存储器事务、I/O事务、配置事务和消息事务。事务分为三个类别:posted(不需要响应,不需要返回完成包,存储器写和消息属于此类事务),非posted(需要响应)和完成包。本文引用地址:http://www.eepw.com.cn/article/190176.htm

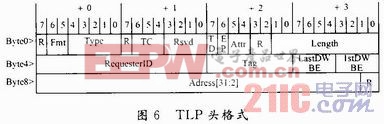

本文设计的基于Wishbone的PCI Express接口的读写操作针对存储器空间,其中存储器读写操作TLP头的格式如图6所示。类型字段(Fmt)为00000b时表示存储器读或者写;格式字段(Type)为00/01b时表示3DW/4DW的存储器读操作,为10/11b时表示3DW/4DW的存储器写操作。

2 基于Wishboen的PCI Express接口实现

2.1 实现原理

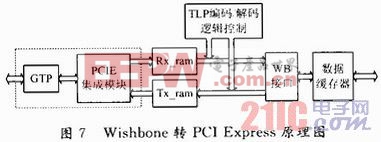

本文基于Xilinx FPGA的PCI Express集成硬核端点模块和Wishhone片上总线,实现了主机和外接存储器问通过PCI Express的接口通信。PCI Express接口基于协议包传输机制,因此,集成端点模块的数据传输均以TLP包的形式进行。实现数据传输可通过以下步骤进行(以PCI Express读传输为例):

(1)待传输数据存储在应用模块中的数据缓存器中,数据缓存器可以使用片外存储器也可以使用片内RAM资源。本设计使用的是片内RAM资源;

(2)数据通过集成在存储器端的Wishbone总线输入到数据缓存区(Tx_ram)中,在数据缓存区(Tx_ram)中根据规定格式形成TLP包;

(3)根据PCI Express协议,将在数据缓存区(Tx_ram)中的TLP包通过集成端点模块发送出去。

PCI Express写传输是上述的逆过程。

其原理框图如图7所示。

2.2 设计买现

Xilinx的V5/V6系列FPGA提供了一个PCI Express硬核端点模块,此端点模块提供了一个PCI Express接口通信的底层配置,但没有包含对TLP包的编码及解码逻辑。因此,需要在设计中实现TLP包的编码及解码逻辑功能。编码是将来自Wishbone片上总线的数据打包成TLP格式存入Tx_ram;解码即是在Rx_ram中提取TLP包的有效载荷。在解码逻辑中,最重要的就是要根据包头的类型字段和格式字段来正确确定事务的类型、头的大小、有效载荷是否存在。

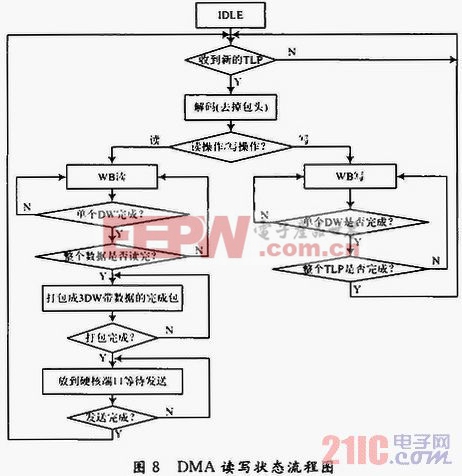

在应用模块的存储器端和FPGA端点IP核之间实现Wishbone的点对点连接,存储器端接口为主端口,与硬核接口端为从端口。实现了32 b/16 b/8 b的单个存储器的读和写以及主机到应用模块间的DMA传输。需要注意的是,在Wishbone读/写操作的时候,一个时钟周期只能进行一个双字的传送,对多个双字进行读写时需要多个时钟周期。

主机到应用模块间的DMA传输包括DMA写操作和DMA读操作,其状态流程如图8所示。

评论