多惯组脉冲输出同步计数系统设计

摘要:为满足某惯导设备生产厂家对多个惯组产品进行同时测试的需求,设计了一种对于多路脉冲信号同步计数的测试系统。(方法)测试系统以FPGA芯片和USB芯片CY68013为核心,对4个惯导组件输出的48路脉冲信号,每路进行无缝计数,每4ms为一个计数单元。并利用USB总线将每一个计数单元的计数值上传到测控计算机,上位机程序进行实时的处理、保存和显示。(方法)测试系统满足了对多个惯组产品同时测试的要求,提高了测试效率。

关键字:惯导组件;USB;CY68013;FPGA

惯组产品是现代惯导系统最核心的信息源,由陀螺仪和加速度计组合而成。惯组产品工作时直接输出脉冲信号。测试过程采用专用测试平台,将产品固定在带温箱的三轴转台上,通过在不同的温度下改变转台的位置和速率,由测试系统对其输出的脉冲信号进行计数,再对计数值根据数学模型进行处理,从而得到惯组产品的性能参数。由于温度是影响惯导组件的主要因素之一,所以需要在多个温度点下,对其进行多次测试。而每个温度点需要4个小时的保温。因而完成一个产品的标定,一般需要三天左右的时间才能完成。针对这种情况,本文提出了一种多惯组同时测量的方案,利用FPGA对脉冲信号进行采集,再通过USB总线把采的数据发送到PC机上进行数据归算。与传统的测量系统相比,本系统可以对4个惯导组件的48路脉冲数据进行同步计数并输出,进而有效地缩短测试周期,提高测试效率。

1 测试系统组成

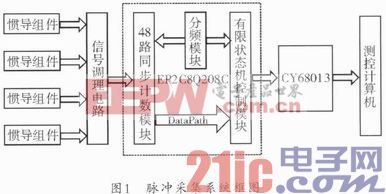

多惯组脉冲测试系统是由下位机和上位机两个部分构成。下位机由FPGA和USB接口电路组成,实现对脉冲信号的计数和数据的接收。上位机是MFC程序设计的界面,对接收到的数据进行实时的处理、显示和保存。由于本系统是同时接收4套惯组48路脉冲信号,所包含的计数器个数多,计数频率高,并且分别对48路信号独立测量,要求较高的可靠性,所以系统采用FPGA来实现控制逻辑及计数模块的功能。系统选用Altera公司的Cyclone IIEP2C89208C8N型号的FPGA芯片。在数据传输方面,选用Cypress公司的FX2LP CY68013芯片作为USB传输模块。采集系统框图如图1所示。

在图1中,通过Verilog语言对48路同步计数模块进行设计,实现对48路脉冲信号的同步计数,将接收到的数据通过USB芯片CY68013发送到PC机,由PC机对接收到的数据进行处理,脉冲信号的计数是由无缝计数器,每隔4ms向48路计数模块发送相应的地址,获得48路脉冲计数模块的计数值,再通过USB总线把数据发送到PC机上。

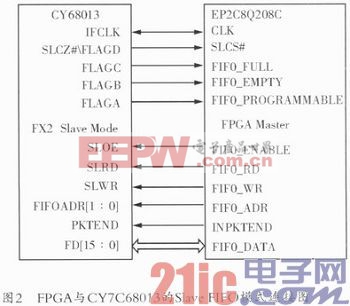

FX2LP CY68013芯片有PORTS、Slave FIFOs和GPIF三种接口方式:PORTS模式以CY68013自带的8051核来进行端口FIFO的读写,其优点是开发简单,缺点是传输速度有限;Slave FIFOs模式是使用外部芯片的逻辑来直接操作端口FIFO,其优点是端口FIFO操作灵活,缺点是传输速度依赖于外部控制逻辑的速度;GPIF模式是使用波形编辑工具生成的波形信号来进行端口FIFO的读写,其优点是传输速度最高,缺点是读写逻辑单一,不容易灵活控制。因为是对48路脉冲信号进行实时采样计数,且每一路脉冲信号采用一个16位计数器,采样周期为4毫秒,即每秒要采集250次。但在实际使用中发现,在PORTS模式下,由于8051内核执行速度有限,在极短的中断时间内有时会不能完成其数据处理和传输的任务,此种状态下USB端就会出现死循环状态。但在Slave FIFO或CPIF模式下,传输和接收的端口将不经过8051内核干涉即可同片外高速互传数据,从而提高接收发送串行信号的效率与可靠性。由于GPIF模式下的编辑波形只能进行读写操作,而在Slave FIFOs的模式下状态机可以对数据进行简单的处理。因此,本系统使用Slave FIFOs的传输模式。

2 系统的FPGA设计

2.1 48路脉冲计数模块设计

系统的48路脉冲计数模块设计是通过使用Verilog语言编写的16位计数器,可以对惯导组件输出的信号分别进行不间断计数,计数值读取过程不影响计数器的正常计数,该模块data_in[47…0]是48路惯导组件的脉冲输入,add_in [6…0]是每个脉冲输入通道的地址,data_out[15…0]是计数单元的计数值输出。

评论