基于FPGA的DES加密算法的高性能实现

随着通信系统和网络的快速发展,要求数据的通信、处理和存储的安全性和可靠性越来越高。开发安全加密机器,要求具备实时加密,可改变密钥,使用多种算法等性能,因此可重用、参数化的加密核成为一种理想的安全加密设计。

目前加密算法有单密钥和公用密钥2种体制。单密钥体制中最著名的是DES加密算法,它是目前应用广泛的分组对称加密算法,广泛应用于卫星通信、网关服务器、视频传输、数字电视接收等方面。文献指出,尽管软件实现的DES加密算法容易改变,但是其数据处理速率低;专用集成电路ASIC可提供高性能算法但灵活性差;而FPGA实现的加密算法具有对同一个FPGA使用不同算法的重新编程可增加其灵活性,使用同一个算法的不同版本和改变结构参数实现系统升级。因此利用FPGA实现DES加密算法是一种理想选择并具有实际的应用价值。

为了克服传统DES加密算法流水线的FPGA实现的子密钥需先后串级计算,密钥不能动态刷新的缺点,提出一种新的加密算法,提高DES FPGA实现系统的处理速度,增加系统的密钥动态刷新功能,提高系统的可重用性。

2 DES加密算法原理

DES加密算法是将64位的明文输入块变为64位的密文输出块,其密钥是64位,其中8位是奇偶校验位。整个算法的处理流程如图1所示。

从整体结构来看,DES加密算法可分为3个阶段:

(1)对于给定的明文m,通过一个(固定的)初始置换IP重新排列m中的所有比特,从而构造比特串m0。把64位比特串m0拆分成左右2个部分,即m0=IP(m0)=L0R0,这里L0由m0的后32位组成。

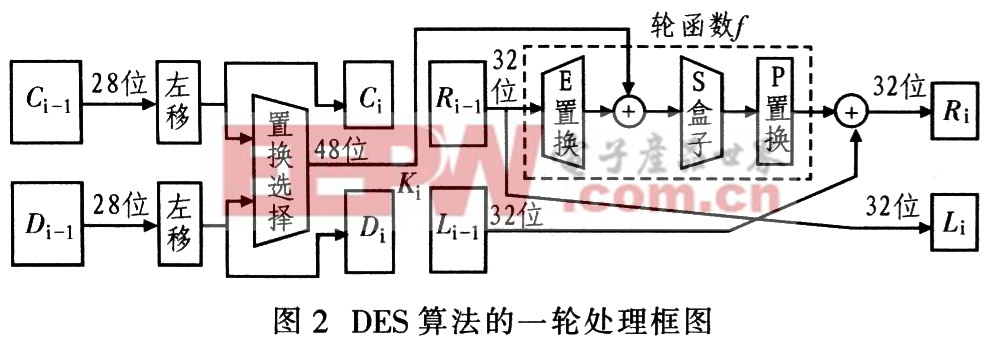

(2)计算16次迭代变换,所有16次迭代具有相同结构。第i次迭代运算是以前一次迭代的结果和由用户密钥扩展的子密钥Ki作为输入;每一次迭代运算只对数据的右半部分Ri-1进行变换,并根据以下规则得到LiRi作为下一轮迭代的输入![]() 表示2个比特串的异或(按位模2加)。其中每一轮次运算的子密钥Ki是将56位密钥分成2个部分,每部分按循环移位次数表移位并按置换选择表置换得到。轮函数f的处理过程:先将Ri-1进行E置换,再与本轮的子密钥相异或,最后将S盒字替换和P置换。图2是DES算法的一轮处理框图。

表示2个比特串的异或(按位模2加)。其中每一轮次运算的子密钥Ki是将56位密钥分成2个部分,每部分按循环移位次数表移位并按置换选择表置换得到。轮函数f的处理过程:先将Ri-1进行E置换,再与本轮的子密钥相异或,最后将S盒字替换和P置换。图2是DES算法的一轮处理框图。

(3)对16次迭代变换的结果使用IP置换的逆置换IP-1,最后所得到的输出即为加密后的密文。

3 DES加密算法的FPGA实现

3.1 系统总体设计

DES加密算法是以多轮的密钥变换轮函数和密钥+数据运算轮函数为特征,与之相对应的硬件实现.既可以通过轮函数的16份硬件拷贝,达到深度细化的流水线处理,实现性能优化,即性能优先方案;也可通过分时复用,重复调用一份轮函数的硬件拷贝,以时间换空间,从而得到硬件资源占用上的最小化,即资源优先方案。考虑到加密系统首先需满足实时处理要求,因此选用速度性能优先方案。

DES算法的迭代特征使其适用于采用循环全部打开和流水线结构设计。由于提前生成子密钥,并且用逻辑电路完成S盒设计,就可以解开DES算法的16次循环迭代为16级流水线数据块加密,实现16个数据块同时加密。这样,从第1个数据块开始加密,经16轮次延时后,每一轮次延时都会有一个数据块编码完成输出一个密文块。这样它的加密速度是循环式加密的16倍,而代价是面积增加16倍,但考虑到每个轮次都是组合逻辑运算,占用面积小,这样的代价完全能够接受。图3是基于子密钥预计算的DES算法流水线处理原理图。

评论