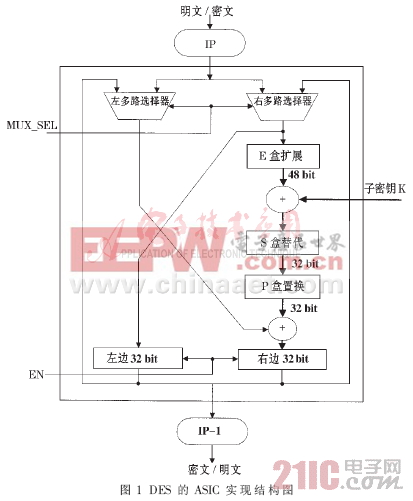

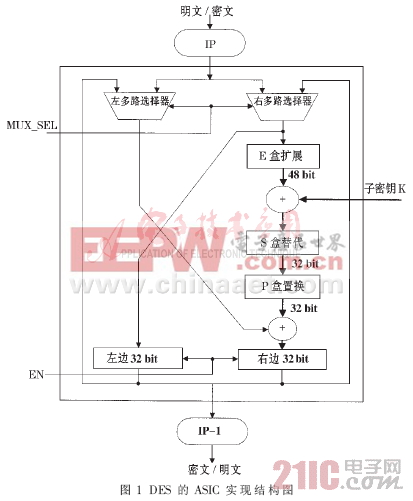

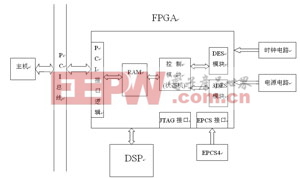

- 一种基于FPGA的数据加密标准算法的实现。就资源优先和性能优先分别使用循环法和流水线法对DES加密算法进行了设计,并对其进行了比较。通过采用子密钥简单产生和ROM优化S盒的方法,对流水线法进行改进,达到了资源占用率低、加密速度快的效果。

- 关键字:

数据加密标准算法 DES FPGA 流水线

- 为了确保数据从数据源安全传输到目的地,必须在安全应用中采用加密技术。最常用的加密技术采用确定性算法,并对固定长度数据块进行固定不变的转换操作。此类加密技术包括高级加密标准(AES)、数据加密标准(DES)、国际数据加密算法(IDEA)和RC5等。然而,这种“分组密码”方案会制约硬件的吞吐量、数据处理和缓冲容量,因为加密操作必须在下个数据块到来之前完成。大量工业加密

- 关键字:

AES IDAE DES RC5

- 目前在金融界及非金融界的保密通信中,越来越多地用到了DES算法。DES(Data Encryption Standard)即数据加密算法 ...

- 关键字:

单片机 汇编语言 DES 加密算法

- DES算法全称为Data Encryption Standard,即数据加密算法,它是IBM公司于1975年研究成功并公开发表的。DES算法的入口参数有三个:Key、Data、Mode。其中Key为8个字节共64位,是DES算法的工作密钥;Data也为8个字节64位,是

- 关键字:

des 算法原理

- 1 引言 美国Atmel公司生产的AT94K系列芯片是以Atmel0.35的5层金属CMOS工艺制造。它基于SRAM的FPGA、高性能准外设的Atmel8位RISCAVR单片机。另外器件中还包括扩展数据和程序SRAM及器件控制和管理逻辑。图1-1是Atme

- 关键字:

解密 分组 设计 AES 基于 DES FPSLIC

- 介绍了DES算法原理,详细分析了子密钥生成、S盒和轮函数的设计。将DES算法采用资源优先方案,在轮函数内部设置流水线架构,提高了整体处理速度;简化子密钥与原始密钥的生成关系,实现子密钥在迭代过程的动态分发;利用双重case语句实现S盒的变换功能,加快算法执行速度。运用硬件描述语言Verilog,采用自顶向下的设计思想,在FPGA平台上实现了改进DES算法的功能。

- 关键字:

FPGA DES 算法

- 针对DES密码芯片的CPA攻击仿真设计方案, 摘 要: 为研究密码芯片抗功耗分析性能,构造了一个功耗分析研究平台,结合DES算法在平台上进行了相关性功耗分析(CPA)攻击仿真实验。根据猜测部分密钥时的模拟功耗与猜测整个密钥时模拟功耗之间的相关系数大小来

- 关键字:

仿真 设计 方案 攻击 CPA DES 密码 芯片 针对

- 摘要:为研究密码芯片抗功耗分析性能,构造了一个功耗分析研究平台,结合DES算法在平台上进行了相关性功耗...

- 关键字:

功耗分析 仿真平台 DES 密码芯片

- 利用汇编语言实现DES加密算法,DES算法是一种数据加密算法。自从1977年公布以来,一直是国际上的商用保密通信和计算机通信的最常用的加密标准。DES算法的实现一般用高级语言。

关键词:加密算法 DES 汇编语言

目前在金融界及非金融界的保密通

- 关键字:

加密 算法 DES 实现 汇编语言 利用

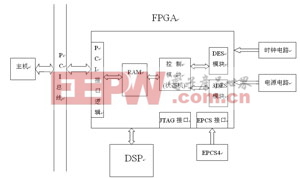

- 基于FPGA的DES、3DES硬件加密技术,传统的加密工作是通过在主机上运行加密软件实现的。这种方法除占用主机资源外,运算速度较慢,安全性也较差。而硬件加密是通过专用加密芯片、FPGA芯片或独立的处理芯片等实现密码运算。相对于软件加密,硬件加密具有

- 关键字:

加密 技术 硬件 3DES FPGA DES 基于

- 1 引言 美国Atmel公司生产的AT94K系列芯片是以Atmel0.35的5层金属CMOS工艺制造。它基于SRAM的FPGA、高性能准外设的Atmel8位RISCAVR单片机。另外器件中还包括扩展数据和程序SRAM及器件控制和管理逻辑。图1-1是

- 关键字:

解密 AES 实现 分组 DES FPSLIC 设计 基于

- 在分析DES算法原理的基础上,详细阐述一种基于VHDL描述、FPGA实现的DES加密算法系统的设计和仿真结果。该系统采用了一种基于子密钥预先计算的新型流水线设计方案,克服了传统DES流水线实现方式的缺点,使系统的密钥可动态刷新.并在硬件资源消耗有所降低的情况下,进一步提高系统的处理速度,系统最高时钟频率为222.77 MHz.信息加密的速度为14.26 Gb/s,是最快软件实现方式的112倍。同时系统还具有设计灵活,可靠性高,可重用性强.升级方便等特点。

- 关键字:

FPGA DES 加密算法 性能

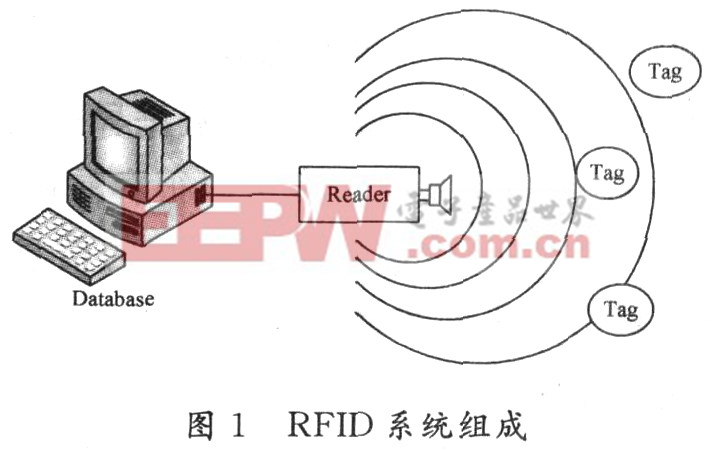

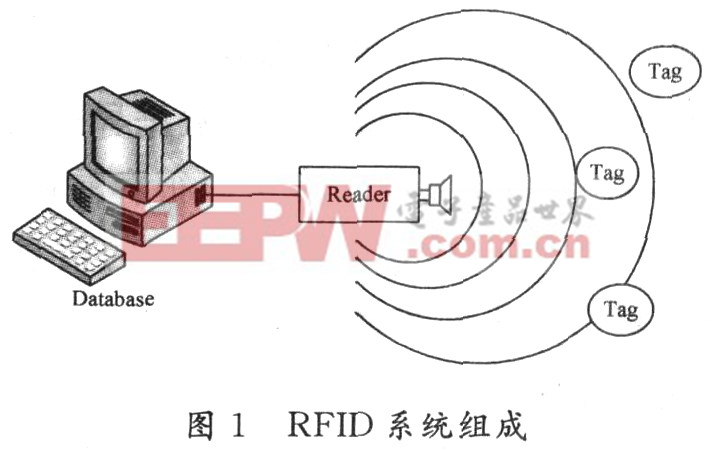

- 摘要:作为一种非接触式的自动识别技术,射频识别(RFID)技术在社会生活中起到越来越重要的作用,但是安全隐患的存在制约了RFID的广泛应用。分析了现有的RFID安全机制,在EPCglobal UHF协议规定的基础上,提出了针对标

- 关键字:

系统 设计 安全 RFID DES 算法 基于

des介绍

DES是一种对二元数据进行加密的算法数据分组长度为64位密文分组长度也是64位.使用的密钥为64位有效密钥长度为56位(有8位用于奇偶校验)。解密时的过程和加密时相似但密钥的顺序正好相反。DES的整个体制是公开的系统的安全性完全靠密钥的保密。

DES算法的过程是在一个初始置换IP后明文组被分成右半部分和左半部分,每部分32位,以L0和R0。表示然后是16轮迭代的乘积变换,称为函数f,将数 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473