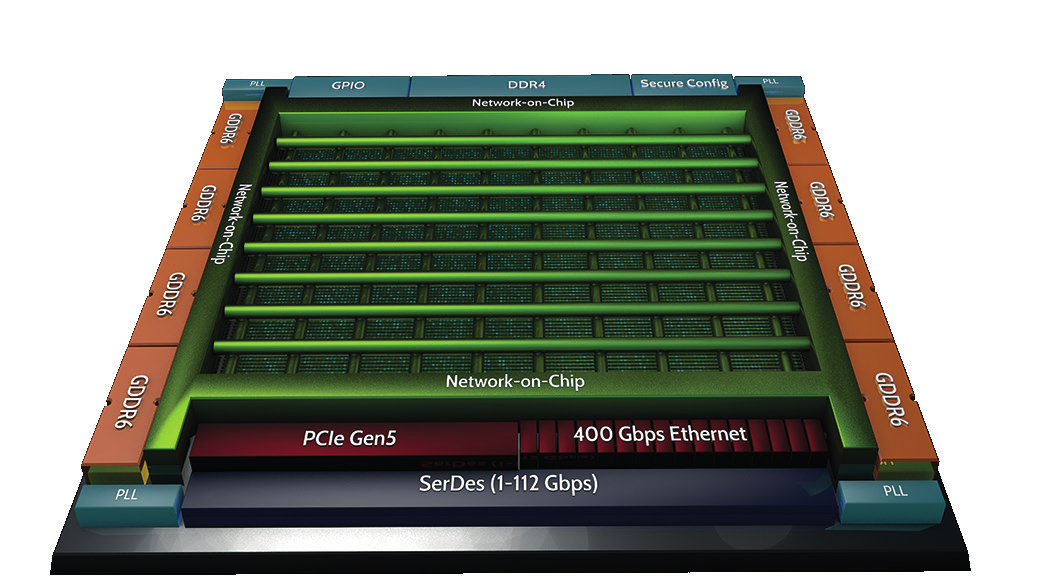

- Achronix 最新基于台积电(TSMC)的7nm FinFET工艺的Speedster7t FPGA器件包含了革命性的新型二维片上网络(2D NoC)。2D NoC如同在FPGA可编程逻辑结构上运行的高速公路网络一样,为FPGA外部高速接口和内部可编程逻辑的数据传输提供了超高带宽(~27Tbps)。图1 Speedster 7t FPGA结构图NoC使用一系列高速的行和列网络通路在整个FPGA内部分发数据,从而在整个FPGA结构中以水平和垂直方式分发数据流量。NoC中的每一行或每一列都有两

- 关键字:

3DES 超高带宽

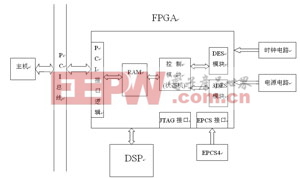

- 基于FPGA的DES、3DES硬件加密技术,传统的加密工作是通过在主机上运行加密软件实现的。这种方法除占用主机资源外,运算速度较慢,安全性也较差。而硬件加密是通过专用加密芯片、FPGA芯片或独立的处理芯片等实现密码运算。相对于软件加密,硬件加密具有

- 关键字:

加密 技术 硬件 3DES FPGA DES 基于

- 基于ARM的3DES加密算法实现,3DES算法是一个重要的对称加密算法,被广泛应用于实际系统中。目前并没有针对嵌入式的实现方法,依据3DES算法和一般嵌入式系统需求,详细介绍该系统硬件和软件的设计过程。硬件以三星公司的S3C2410处理器为核心,系统以嵌入式Linux为载体。在此详细阐述开发环境的搭建、Bootloader的架构及功能、内核及文件系统的编译和移植。基于系统硬件和软件设计过程,通过MiniGUI图形界面对3DES算法进行了演示。

- 关键字:

算法 实现 加密 3DES ARM 基于

- 随着网络的快速发展,信息安全越来越引起人们的关注。加密技术作为信息安全的利器,正发挥着重大的作用。通过在硬件设备(如由器、交换机等)中添加解密功能,可使存储和传输的数据具有较高的安全性。传统的加密工作是通过在主机上运行加密软件实现的。这种方法除占用主机资源外,其运算速度较硬件加密要慢,密钥以明文的方式存储在程序中,或者以加密的方式存储在文件或数字库中,重要数据(如个人密码PIN等)会在某一时刻以明文形式出现在计算机的内存或磁盘中,安全性较差。而硬件加密是通过独立于主机系统外的硬件加密设备实现的,所有关键数

- 关键字:

3DES FPGA设计 单片机 加密算法 嵌入式系统 状态机

3des介绍

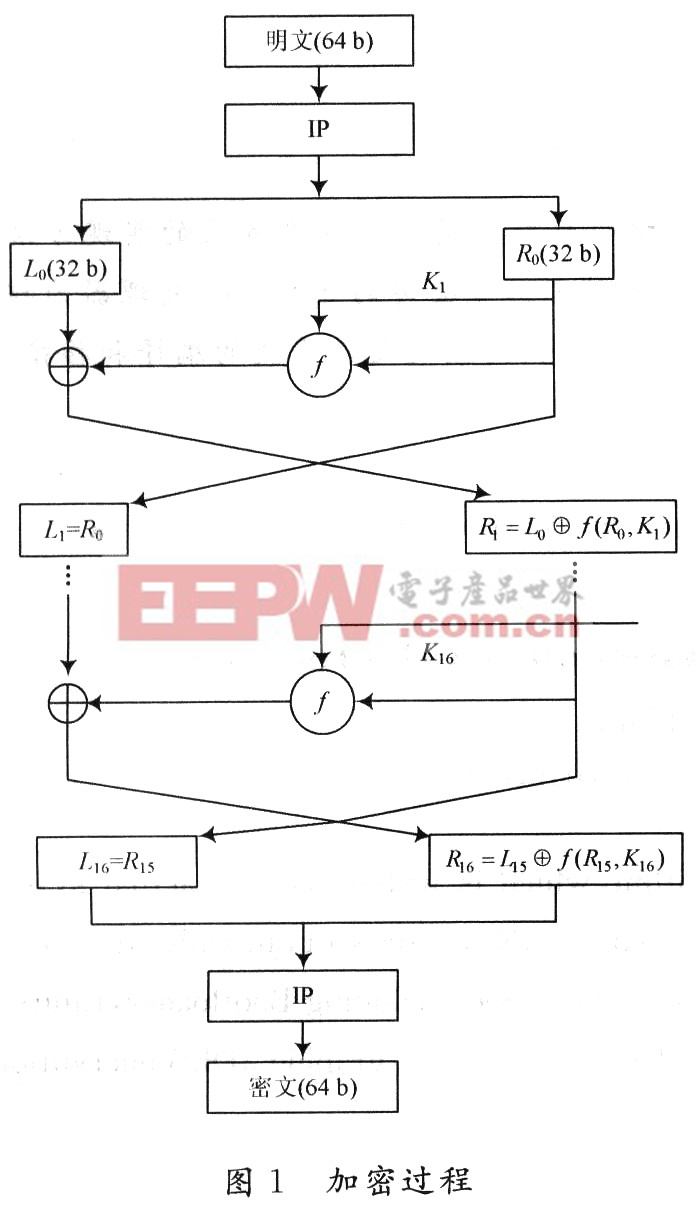

3DES(或称为Triple DES)是三重数据加密算法(TDEA,Triple Data EncryptiON Algorithm)块密码的通称。它相当于是对每个数据块应用三次DES加密算法。由于计算机运算能力的增强,原版DES密码的密钥长度变得容易被暴力破解;3DES即是设计用来提供一种相对简单的方法,即通过增加DES的密钥长度来避免类似的攻击,而不是设计一种全新的块密码算法。 3DES [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473