基于FPGA的AD9910控制设计

随着数字信号处理和集成电路的发展,要求数据处理速度越来越高,基于单片机+DDS(直接数字频率合成)的频率合成技术已不能满足目前数据处理速度需求。针对这一现状,本文提出了基于FPGA+DDS的控制设计,能够快速实现复杂数字系统的功能。

1 AD9910的硬件电路设计

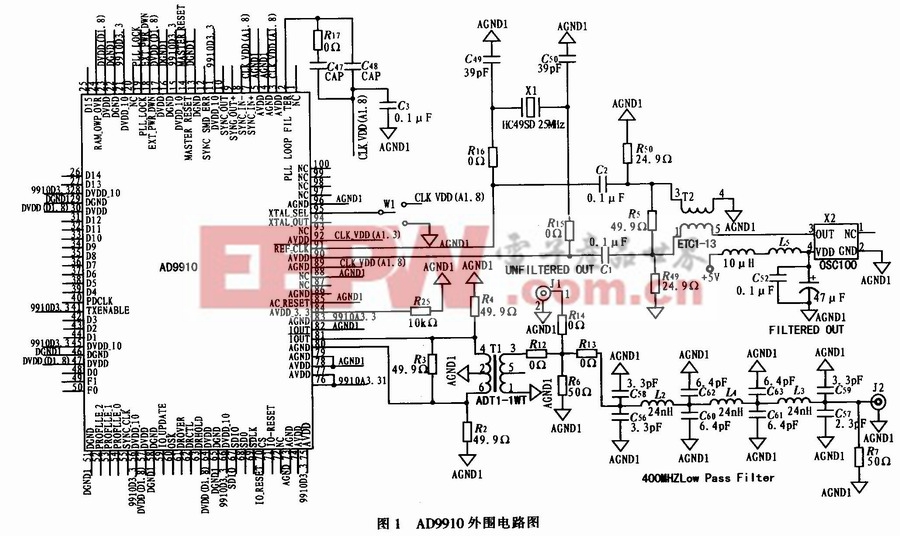

AD9910是ADI公司推出的一款单片DDS器件,内部时钟频率高达1GHz,模拟输出频率高达400 MHz,14-bit的DAC,最小频率分辨率为0.23 Hz,相位噪声小于-125 dBc/Hz@1 kHz(400 MHz),窄带无杂散动态范围大于80 dB,串行I/O控制,具有自动线性和随机的频率、相位和幅度扫描功能,1 024 32位RAM,具有调幅、调相的功能,1.8 V和3.3 V供电,可实现多片同步。应用在高灵敏度的频率合成器、可编程信号发生器、雷达和扫描系统的FM调制源、测试与测量装置以及高速跳频系统AD9910芯片的主要外围电路为:参考信号源、控制、环路滤波器和输出低通滤波器等电路。参考信号源为AD9910提供基准频率,参考信号输入芯片后,内部的倍频器和锁相环起作用产生1GSPS的系统时钟;控制电路通过芯片的I/O给内部寄存器写入内容,寄存器内容不同,芯片工作状态不同,控制芯片可以是单片、FPGA或DSP,本设计采用FPGA;

AD9910提供专门的管脚外接环路滤波器,以优化内部PLL的性能,环路滤波器为简单的低通滤波器;AD9910输出高达400 MHz的模拟信号,为了减少噪声,在它的输出端口设计了400MHz的低通滤波器。

图1为实际设计的AD9910外围连接图。

在AD9910的电路设计中,应注意以下几个问题:

1)AD9910电源和地设计。AD9910需要4组电源,AVDD(1.8 V)、DVDD(1.8 V)、AVDD(3.3 V)和DVDD(3.3 V),模拟电源和数字电源需要隔离,电源管脚的滤波最好采用钽电容和陶瓷电容。在PCB设计中,数字地和模拟地分开,用磁珠单点连接,减少干扰。

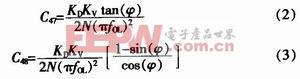

2)AD9910环路滤波器设计。当外部的时钟较低时,例如100 MHz,系统时钟1 GHz,芯片内部的锁相电路起作用,这时需要在外部设计环路滤波器,如图1中R17、C47和C48构成的RC滤波器,电容电阻值用如下公式计算。

![]()

其中:N为分频比,KD为鉴相器的增益,KV是VCO的增益,fOL是环路带宽。

3)晶振电路的设计。AD9910需要外部提供参考信号源,它的质量直接决定了模拟输出信号的质量(频率精度和相位噪声),本设计采用高精度的温补晶振,频率100 MHz。在PCB设计时尽量靠近时钟管脚。

2 FPGA控制AD9910的软件实现

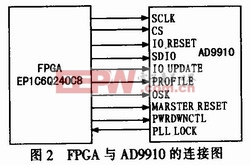

采用Ahem公司的EP1C6Q240C8控制AD9910,该器件的外部时钟频率为50 MHz,20个128?36 bit的RAM块,5980个逻辑单元(LE),240个管脚,属表贴器件。

FPGA与AD9910的外围电路简单,无需外加任何驱动电路,从而节省了硬件电路设计和调试的时间,FPGA与AD9910的连接框图如图2所示。

评论