一种高阶音频均衡滤波器的设计实现

音频均衡器作为高品质音响不可或缺的关键附属调节设备,在音效调整修饰方面起着至关重要的作用。一般音频均衡器有数字和模拟两种实现方法,模拟方法用有源和无源滤波器组实现,受器件温度等特性的影响,难以达到较高的可靠性和一致性,且成本较高。数字实现方法采用数字滤波器,具有较高的灵活性和可靠性。常用的数字滤波器有IIR和FIR两种。IIR滤波器结构简单,所需的存储空间小,但其相位是非线性;FIR滤波器是线性相位滤波器,这对高品质音效处理是必要的。本文通过在FPGA内设计了1 024阶FIR滤波器实现数字均衡滤波,通过系数的重载实现多种频率响应的均衡特性。

本文引用地址:https://www.eepw.com.cn/article/187575.htm1 总体概述

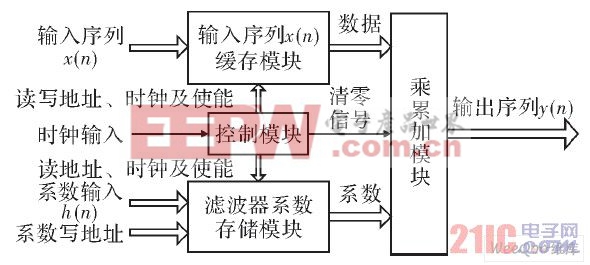

文中设计的FIR音频均衡滤波器采用多相滤波结构,用时间换取空间,节省FPGA内部资源,以达到在固定资源下的最大阶数。实现结构框图如图1所示。

图1 数字滤波器实现结构框图

输入序列以及滤波系数分别存储在缓存阵列中,在时钟同步下由控制模块通过生成相应的读写地址及使能信号,使其按照一定次序输出到乘累加模块进行运算,并输出最终结果。系数可通过外部输入重载,以实现不同的均衡特性。EP1C3系列FPGA共有13个M4K块,每个为256 ×18位,取数据和系数的位宽为16位。为了充分利用有限资源,并考虑处理速度及音频信号速率要求,取每个缓存子模块的存储深度为256,即将乘累加模块复用256次,每256个系统时钟周期运算一个采样点数据,输出一个滤波结果。每个缓存子模块占用一个M4K块,连续4个子模块串联,就可实现256 x4=1 024阶的要求,再考虑系数占用的空间,总共消耗8个M4K块。这也是在有限资源下能实现的最高阶数。

2 各模块实现

2.1 输入序列缓存模块

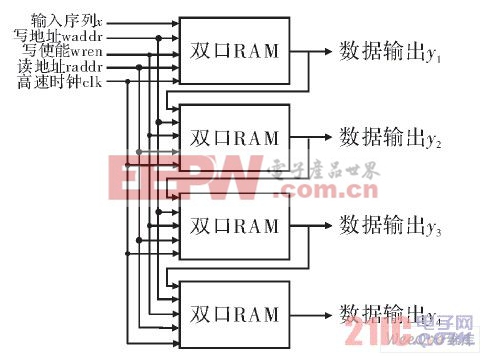

输入序列缓冲模块采用双口RAM模块实现,将4个级联使用,如图2所示。4个子块使用相同的读写地址及使能信号,采样数据从第一个子块输入,第一个子块的数据输出端与下一级子块的输入端直接相连,依次类推。每个缓存子块的数据y1~y4都输出给乘累加模块进行运算。

图2 输入序列缓冲模块实现框图

该模块的关键是读写地址的控制,写地址waddr必须滞后读地址raddr一个时钟周期,这样子块当前输出数据会在下个时钟写入下一个子块的相应单元。256个周期后,子块的数据整体移到下一个子块。

评论