基于单片机和FPGA的扫频仪设计

一个网络的频率特性包括幅频特性和相频特性,在系统设计时,各个网络的频率特性对该系统的稳定性、工作频带、传输特性等都具有重要影响。实际操作中,扫频仪大大简化了测量操作,提高了工作效率,达到了测量过程快速、直观、准确、方便的目的,在生产、科研、教学上得到广泛运用。本设计采用数字频率合成技术产生扫频信号,以单片机和FPGA为控制核心,通过A/D和D/A转换器等接口电路,实现扫频信号频率的步进调整、数字显示及被测网络幅频特性与相频特性参数的显示。

1 系统总体方案及设计框图

1.1 系统总体方案

将输出频率步进可调的正弦扫频信号源作为被测网络的激励Vi,可得被测网络的响应为V0。通过测量各频率点的幅度就可得到V0和Vi的有效值,两者之比就是该点的幅度频率响应;对V0和Vi进行过零比较、整形,再送到FPGA测量相位差,即可得到相频特性。

设激励信号Vi=x(n)=Acos(ω0n+f),稳态输出信号V0=y(n)。利用三角恒等式,可将输入表示为两个复指数函数之和:![]() ,式中,

,式中,![]() 。对于输入为

。对于输入为![]() ,线性时不变系统稳态输出为

,线性时不变系统稳态输出为![]() 。根据线性性质可知,输入g(n)的响应v(n)为:

。根据线性性质可知,输入g(n)的响应v(n)为:![]() 。同理,输入g*(n)的输出v*(n)是v(n)的复共轭。于是得到输出y(n)的表达式:

。同理,输入g*(n)的输出v*(n)是v(n)的复共轭。于是得到输出y(n)的表达式:

因此。输出信号和输入信号是频率相同的正弦波,仅有2点不同:1)振幅被![]() 加权,即网络系统在ω=ω0的幅度函数值;2)输出信号的相位相当于输入有一个q(ω0)时延,即网络系统在ω=ω0的相位值。该方案幅度和相位测量的控制都通过FPGA实现,能够使测量结果精确。

加权,即网络系统在ω=ω0的幅度函数值;2)输出信号的相位相当于输入有一个q(ω0)时延,即网络系统在ω=ω0的相位值。该方案幅度和相位测量的控制都通过FPGA实现,能够使测量结果精确。

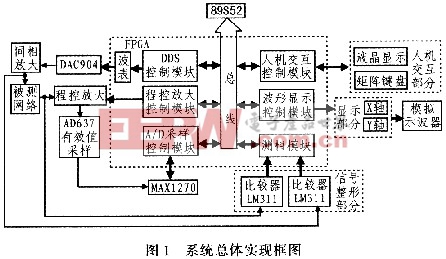

1.2 系统总体设计框图

系统通过键盘扫描得到外界设置的扫频范围和频率步进,通过调用DDS控模块控制DAC904,输出扫频信号。由于信号在被测网络阻带内会有很大的衰减,故用程控放大处理经被测网络的扫频信号之后,利用AD637进行有效值采样,LM311进行整形。信号有效值经MAXl270进行AD转换后得到有效值的数字量,整形后的信号经测相模块处理得到相位差值。在FPGA中写入2个RAM存放被测信号的有效值和相位差值。完成一次扫频后通过波形显示模块将幅频、相频曲线显示在示波器上,并将特定频率点的幅度和相位差值在液晶显示器上进行显示。系统实现框图如图1所示。

2 系统功能部分设计

2.1 扫频信号的产生

直接数字合成(DDFS)信号源。它是一种完全数字化的方法:先将一个周期的正弦波(或者其他波形)的离散样点幅值的数字量预先存储于ROM或者RAM中,按一定的地址增量间隔读出,经D/A转换后成为不同频率的模拟正弦波信号波形,再经低通滤掉毛刺即可得到所需频率的输入信号。按此原理,DDS可以合成任意波形,且可以精确控制相位,频率也非常稳定。利用FPGA制作起来相当容易,且扫频步进实现简单。设FPGA内部的参考频率源的频率为fclk,采用计数容量为2N的相位累加器(N为相位累加器的位数),频率控制字为M,则DDS系统输出信号的频率fout=fclk/2N×M。频率分辨率为:△f=fclk/2N。

评论