大容量FLASH在单片机台标系统中的应用

1 引 言

本文引用地址:https://www.eepw.com.cn/article/172136.htmFLASH是一种兼有紫外线擦除EPROM和电可擦可编程只读存储器(E2PROM)两者优点的新型非易失存储器。由于它可在线进行电可擦除和编程,芯片每区可独立擦写至少10,000次以上,因而对于需周期性地修改被储存的代码和数据表的应用场合,以及作为一种高密度的、非易失的数据采集和存储介质,FLASH都是理想的器件选择。随着其容量越来越大,FLASH对于数字图像的存储也具有了一定的能力。笔者所做的台标机就是用Intel公司生产的64Mbit(8MByte)的FLASH 28F640J5作为台标图像的存储介质。下面就以该台标机系统为例,介绍28F640J5在系统中的具体应用。

2 FLASH28F640J5简介

2.1 主要性能特点

28F640J5是一种采用ETOXⅡ工艺制成的56引脚的快擦写可用电擦除可编程存储器,由于首次使用了每单元存储两位的技术,因而每位占用的或非门资源更少,性能价格比更高。芯片采用分块结构分成64块,每块128kB,这个特性允许用户对其中任意一块数据进行擦除或编程,每块擦除时间仅需1秒。在块擦除过程中如果需要中断擦除操作,可暂停擦除,待处理完其它事后再继续擦除。28F640J5仅需+5V供电电压,工作电流不大于80mA,典型值为 40mA,备用状态时不大于125μA,典型值为80μA,三态输出,与TTL电平兼容。可循环擦写次数为10万次,一般商业品工作温度范围为-20℃~+70℃。

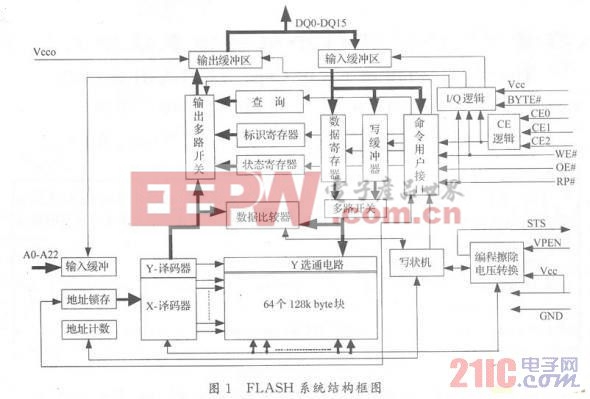

2.2 芯片系统结构及引脚信号

芯片采用一种命令用户接口CUI(CommandUser Interface)和写状态机WSM(WriteState Machine)结构,以此简化模块擦除和编程。命令用户接口是微处理器或微控制器与芯片内部操作之间的界面。无论是模块擦除还是字节编程,只要向CUI 写入两个命令序列,内部的写状态机WSM就会自动地定时执行擦除或编程算法(包括校验操作),从而减轻了微处理器或微控制器的负担。另外,为了指示WSM 的状态和何时以及是否成功完成了模块擦除或字节编程操作,设置了一个状态寄存器SR(State Register)。这样,状态寄存器SR就成了微处理器与写状态机之间的接口。芯片引脚A0-A22为地址线,当为字操作时A0不起作用,A1为最低位地址线。DQ0-DQ7为低字节数据总线,输入数据在输入缓冲区进行编程和写操作,输入命令时在命令用户接口(cui)进行写操作,当状态机忙时DQ6-DQ0不起作用,而状态寄存器的第7位(SR.7)决定状态机的状态。DQ8-DQ15为高字节位数据总线,在字操作模式中使用到。CE0、CE1、CE2为芯片选通信号,当信号有效时,就激活了器件的控制逻辑、输入缓冲器、译码器和敏感放大器,当器件没有选通时,片上电压自动降低到待机电压。RP#为复位或使电压回到待机状态的信号,当RP#为低时,芯片处于待机模式,此时芯片禁止写操作,当RP#为高时可进行读写、擦除等操作,但不要一直将RP#置高,以免影响器件的使用寿命。OE#为输出选通信号,低电平有效,在读周期中,输出缓冲器被选通,数据通过缓冲器输出。WE#为写选通信号。STS为状态位,它显示内部状态机的状态。BYTE#为8位或16 位操作模式选择信号,当BYTE#为低时,器件工作在8位操作模式,DQ8-DQ15挂起,当BYTE#为高时,器件工作在16位操作模式。VPEN是擦除、编程块锁定位操作使能信号,当VPEN<= VPENLK时,存储器的内容不能改变。

3 单片机与芯片接口的设计

因为单片机80C320的地址线只能有16根,仅能寻址64K外存空间。而28F640的内部芯片地址线有23根,所以在设计时对FLASH采取分段设计的方法,设有存储器段寄存器(高位地址寄存器)“WHDZ”。由于单片机的地址空间中既有寄存器,又有存储器,为了方便起见,将单片机的P1.7口定义为寄存器“IO”或存储器访问的区分标志“IORAM”。当“IORAM”为1时,单片机的低八位地址线有效,通过EPLD寻址FLASH的高八位地址(实际为7位),当“IORAM”为0时,单片机80C320寻址存储器低十六位地址空间。这样,单片机的64K外存空间连续寻址配合高位地址寄存器 WHDZ使用,存储器空间的寻址范围可达16MByte。单片机对存储器读写的操作步骤如下:(1)置“IORAM”位,写段地址寄存器“WHDZ”,定义所操作存储器的高位地址。(2)清“IORAM”位,对选择的存储器在段内进行读写。

4 软件设计

28F640J5的操作命令比较多,共有14条,如表1所示。

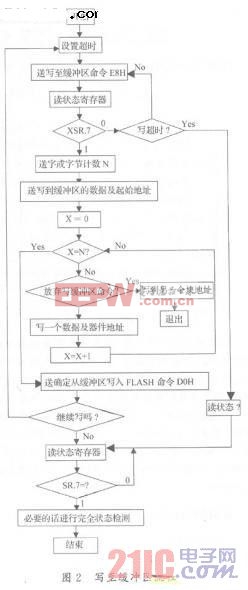

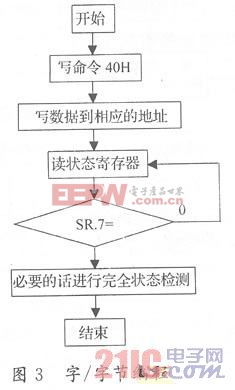

表1中的读阵列、读标识码、读状态寄存器、清状态寄存器、写缓冲区、块擦除、字/字节编程、块擦除挂起、块擦除继续是Intel公司28F系列 FLASH的基本命令集,其它命令为28F640的扩展命令集。Intel28F640 FLASH存储器采用了并行编程技术:在28F640的命令集中由于添加了写缓冲区的命令以及相应的32字节硬件写缓冲资源(程序流程图如图2所示),与传统的字/字节编程方式相比(程序流程图如图3所示),写缓冲区方式一次性可写入32字节,在单片机写入确定写缓冲区数据到FLASH的命令D0H后,再由FLASH以并行编程的方式自动写入,中间无需退出写缓冲区命令。而字/字节编程方式每写入一个数据后需要重新写字/字节编程指令。写缓冲区指令的建立以及并行编程算法的采用,使得写入FLASH的速度比原来提高了近20倍。由于写缓冲区一次最多写入32个字节,所以当器件为字节模式写缓冲区时,计数N =00H-1FH,当器件为字模式写缓冲区时,计数N=00H-0FH。为了最大限度地发挥并行编程的功能,降低器件的功耗,在使用写缓冲区命令时一般将 A4-A0的地址线置为0,也就是编程起始地址为×0,0000B。

在台标机系统中,其台标先是在PC机上用Photoshop、3DMAX等图像处理软件做好,然后由PC机传给台标机。为了保证传送速度采用 57600的波特率,这样,传送一副128行*128列大小的台标仅需13秒左右。尽管28F640采用了并行编程技术,但由于波特率太高,数据并不能及时处理,所以在系统中采用了256K空间的SRAM作为缓冲区。台标图像数据首先在SRAM中存储,待台标图像传送结束再由台标机自身将数据由SRAM写进FLASH。对于满屏图像SRAM并不能完全存储,同时FLASH的地址空间对用户来说并不是完全连续的,芯片的第一块的前四个字节和后面块的前三个字节都为芯片自身所占用,所以在传送满屏图像时采用分块传送的方法,每次传送22行数据,其数据量为720列*22行*4=61.875K,4是指每个像素点信息由R、BG、B、透明度4个字节组成。结合前面设置的FLASH的高八位地址寄存器WHDZ,每传一次改变WHDZ的值。对于满屏图像从FLASH 传送到VRAM(视屏存储器)显示满屏图像也采用分块传送的方式,不过此时传送具体数据的方式不同,单片机并不需要将数据从FLASH一个个读出写往 VRAM,它只需将数据的FLASH起始地址,以及VRAM的开始点和终止点坐标给出,数据传送由硬件采用双字传送实现,从而加快了传送的速度。

5 结束语

在本台标机系统中,我们用8M的FLASH存储器存放了10幅像素点128*128的小台标,4幅动画台标,两幅满屏图像,基本上满足了中小型电视台的要求.随着存储器技术的快速发展,各大芯片厂商一定会推出性能价格比更同、速度更快,容量更大的FLASH存储器。

参考文献

1 何立民,单片机应用系统设计,北京:北京航天航空大学出版社,1992

2 http://www.intel.com.intel 28f640jd datasheet.1998

评论