基于DDS技术的电磁阀检测平台的设计

摘要:为了测试电磁闽在各种工作状态下(即在不同的输入脉冲供电的情况下)的性能,研制了一种模拟电磁阀工作状态的PWM脉冲电源。该电源依靠CPLD构成数字PWM发生器,由单片机控制,具有短路保护和浪涌保护功能。系统软件部分以模块化的方式实现,能够连续地输出不同的PWM脉冲。该电源目前已成功应用到电磁阀的生产企业,为企业创造了显著的经济效益,为我国电磁阀的出口做出了贡献。

关键词:AD9834;单片机;CPLD;占空比

汽车电磁阀在汽车工业生产中需求量极大,模拟电磁阀工作环境,从而检测出其质量的优劣值得关注研究。笔者设计的电磁阀检测平台是基于DDS技术与单片机相结合,同时运用CPID技术,模拟出电磁阀在工作期间的相关参数环境,从而判断电磁阀的好坏。

本设计采用直接数字合成(DDS)技术,采用专用集成芯片AD9834作为三角波产生模块,利用51单片机和CPLD来控制完成整个系统的设计。该系统输出的三角波低频特性好并且可以模拟斜坡信号,能产生可调占空比的方波信号,可调范围达1%~99%。

1 系统设计方案

本文设计的数字信号源的系统框架如图1所示。

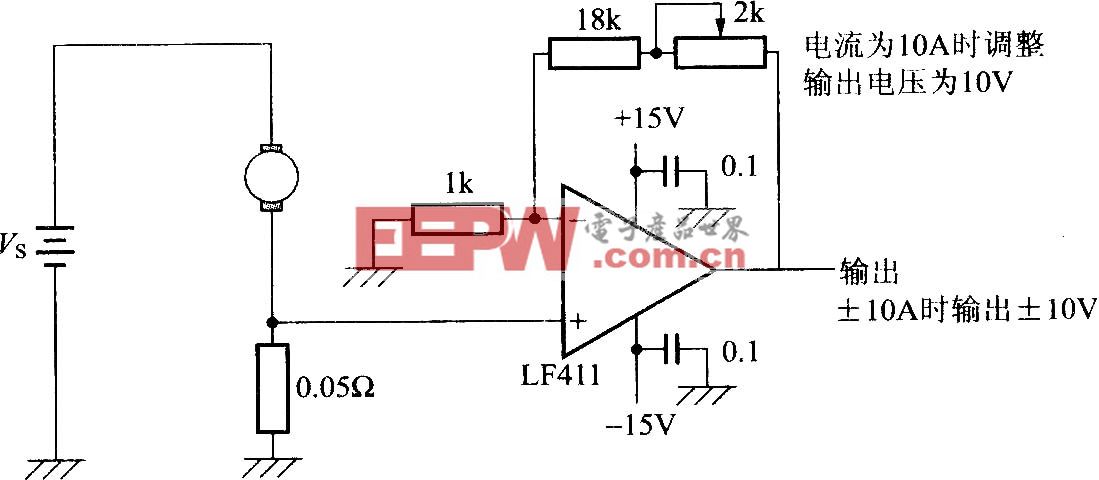

本系统产生输出频率为0~25 kHz,最小精度为1 Hz的信号,占空比在0~100%范围内可调,变化周期为10 s的整数倍。系统输出电压VOUT范围0~40 V,最小精度0.01 V,输出电流最大可达10 A,方波低电压可词范围0~10 V,并且波形较好,可以连续变化,误差不超过1%。

单片机完成键盘扫描和按键处理,通过SPI总线对AD9831进行控制处理,通过AD7541进行采样处理。系统中的CPLD完成对单片机的扩展和测频功能。单片机发出的指令通过CPLD控制DDS以完成信号的产生。

2 模块电路设计

2.1 控制系统

单片机控制整个系统工作,采用12 MHz晶振,P1.0、P1.1、P1.2、P1.3、P1.4、P1.5接一块3x3矩阵键盘,P0口为扩展接口,连接一块8255芯片扩展端口,并且同时连接LCD的DB0、DB1、DB2、DB3、DB4、DB5、DB6、DB7数据控制端口。P2.3、P2.4、P2.5分别接AD98 34的FSYNC、SCLK、SDATA端口。单片机各种数据和命令通过CPLD送出。

单片机向CPLD写数据时,读信号都一直置低电平,写信号口在上升沿时,CPLD开始读地址,写信号口在下降沿时,CPLD开始读数据;单片机从CPLD读数据时,将读信号口一直置低电平,读信号口在上升沿时,单片机开始读地址,写信号口在下降沿时,单片机开始读数据。时序图如图2所示。

2.2 DDS信号产生单元

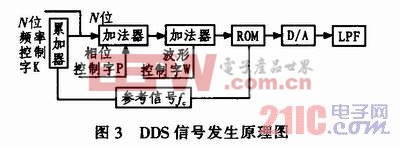

DDS原理:直接数字频率合成器(Direct DigitalSynthesizer)是从相位概念出发直接合成所需波形的一种频率合成技术,一个直接数字频率合成器由相位累加器、加法器、波形存储ROM、D/A转换器和低通滤波器(LPF)构成。DDS框架图如图3所示。

其中K为频率控制字,P为相位控制字,W为波形控制字,fc为参考时钟频率,N为相位累加器的字长,D为ROM数据位及D/A转换器的字长。相位累加器在时钟fc的控制下以步长K作累加,输出的N位二进制码与相位控制字P波形控制字W相加后作为波形ROM的地址,对波形ROM进行寻址,波形ROM输出D位的幅度码S(n)经D/A转换器变成阶梯波S(t),再经过低通滤波器平滑后就可以得到合成的信号波形。合成的信号波形形状取决于波形ROM中存放大幅度码,因此用DDS可以产生任意波形。使用50 MHz的晶振理论上DDS可以产生15 MHz左右的失真度小于1%的正弦信号,信噪比可以达到60 dB,信号的输出频率可以表示为:

f0=(fc/2n)×M

fc为DDS时钟频率;N为相位累加器位数;M为相位累加器步长;f0为输出频率。

低通滤波器相关文章:低通滤波器原理

评论