基于ARM的高精度数据采集系统设计

摘要:针对传统数据采集系统结构复杂,体积大,成本高的问题,设计了一种基于ARM的新型、低成本、高精度数据采集系统,并提出了该系统的设计方案。详细论述了数据采集系统的硬件实现方案、抗干扰措施及控制时序,重点分析了高精度并行A/D的工作时序。实际应用结果表明,该数据采集系统精度高,体积小,成本低,工作性能强,具有较高的实用价值和借鉴意义。

本文引用地址:https://www.eepw.com.cn/article/171426.htm目前,高精度数据采集系统的结构普遍采用DSP+FPGA的构架,系统结构复杂,体积大,成本高,不适用于某些领域的小型化、低成本的特殊要求。综上,设计了一种结构简单,体积小,成本低,采集精度高的数据采集系统,具有非常重要的现实意义及应用前景,能够为国内数据采集系统开发提供一定的经验和参考。

1 数据采集处理系统的工作原理和结构

嵌入式微处理器ARM具有外围配置电路简单、体积小、成本低、性能高、可靠性高和外围硬件资源丰富等优点,能够保证数据采集的实时性,而且还有较强的数据处理功能,在诸多领域的应用日趋广泛。本方案中模/数转换芯片选用16位ADS8364,系统主芯片选用意法半导体公司推出的基于ARM Cortex-M3系列32位芯片STM32F103ZET6,主频为72 MHz,工作电压为2.0~3.6V,I/O电压为3.3V。112个通用I/O端口,3个SPI通信接口,2个I2C通信接口,5个USART通信接口,1个USB接口,1个CAN通信接口,4个通用16位定时器和2个PWM定时器,内置512 KB FLASH ROM和64 KB RAM。

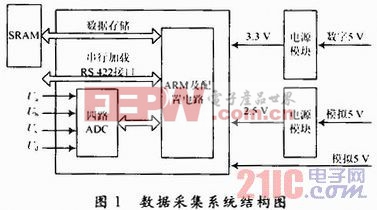

数据采集系统的工作原理:当ARM芯片发出采集指令的时,将模拟信号采集到主芯片中,并进行后续解算,同时将采集到的信息存贮到外置超大SRAM中,以备后期分析处理。系统结构图如图1所示。

2 硬件电路设计

2.1 时钟电路设计

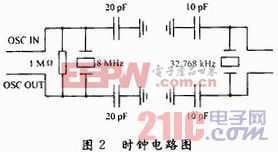

主芯片有2个外部时钟源,电路如图2所示,32.758 kHz的晶体是一个低速外部晶体,它能为实时时钟部件(RTC)提供一个低速但高度精确的时钟源。8 MHz外部晶振作为系统的时钟源,经过倍频后变成72 MHz为ARM提供时钟。

2.2 复位电路

系统复位有多种方式:NRST引脚上出现低电平(外部复位);窗口看门狗计数终止条件(WWDG复位);独立看门狗计数中止条件(IWDG复位);软件重围(SW复位);低电源管理复位。本方案中采用第一种复位方式,只需在外部加复位开关,方式简单,便于操作。

2.3 JETG接口

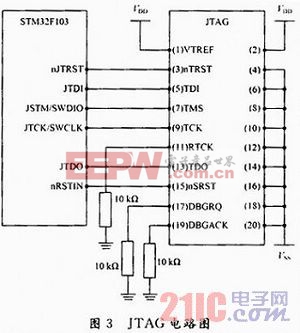

仿真接口为JTAG形式,实现对STM32F103ZET6的仿真与调试。电路图如图3所示。

评论