PAL一体化摄像机设计

摘要:基于ICX229AK CCD芯片组设计了具有VGA接口的一体化摄像机。采用DSP+FPGA+ASIC的构架,完成了视频信号的采集和多格式显示。在FPGA中实现了自动聚 焦、自动光圈等功能,并扩展了鼠标驱动及划线、OSD显示等实用功能。通过PWl226滤波放大处理,完成了PAL制数字视频信号到VGA格式的转换,分 辨率可达到1 024x768。实现了复合视频、S-VIDEO和VGA 3种视频信号的同时输出。该一体化摄像机可用于视频展台及实时监控等方面,大大提高了输出图像质量。

关键词:PAL;VGA;FPGA;自动聚焦;图像放大

一体化摄像机因其体积小巧、价格低廉,安装简便等特点广泛应用于监控、教育、医学等领域。一体化摄像机根据使用对象的情况和要求来进行设计。基于FPGA 器件的可并行处理能力及其可重复编程的灵活性,提出了一种以DSP+FPGA+ASIC为架构的系统解决方案,改善了以往一体化摄像机功能扩展困难的问 题,提高了图像的质量,扩大了其应用范围。

1 系统硬件设计

系统硬件框图如图l所示。视频采集模块采用SONY公司摄像机套件,主要包括470 K像素PAL制CCDICX229AK,AFE(模拟前端)CXA2096N和专用DSPCXD4103。该模块先将CCD采集到的图像数据经DSP处理 后,输出分辨率为748x584的PAL制YUV(422)ITUREC656格式的数字视频信号,同时输出行、场参考信号和像素时钟信号。这些信号先经 过FPGA图像处理模块,实现自动聚焦、4幅图像存储、鼠标驱动及划线功能、实时图像与存储图像上下左右对比、OSD叠加、图像冻结、负片显示、镜像、彩 色黑白选择输出等功能。处理后的信号最终送到视频显示模块,经过专用集成电路(PWl226)处理后产生RGB图像信号及标准SVGA格式的行、场同步信 号,使图像传感器采集的图像可在VGA显示器上实时显示。

1.1 视频采集模块

图2为视频采集模块硬件框图。系统上电后,DSP从EEPROM中读取初始化信息。初始化完成后,DSP产生CCD行、场时序信号,同时 产生AFE(模拟前端)的采样时序信号。CCD在行、场时序作用下,送出采集的原始图像数据,在AFE经过CDS(相关双采样)、AGC(自动增益控制) 后,将量化后的信号送入DSP。DSP内置10 bit的ADC将量化信号转为数字信号,对其进行噪声滤波、电平箝位、自动白平衡、边缘增强等处理后,输出PAL制YUV(4:2:2)格式的数字视频信 号。同时DSP直接输出复合视频及S-VIDEO。

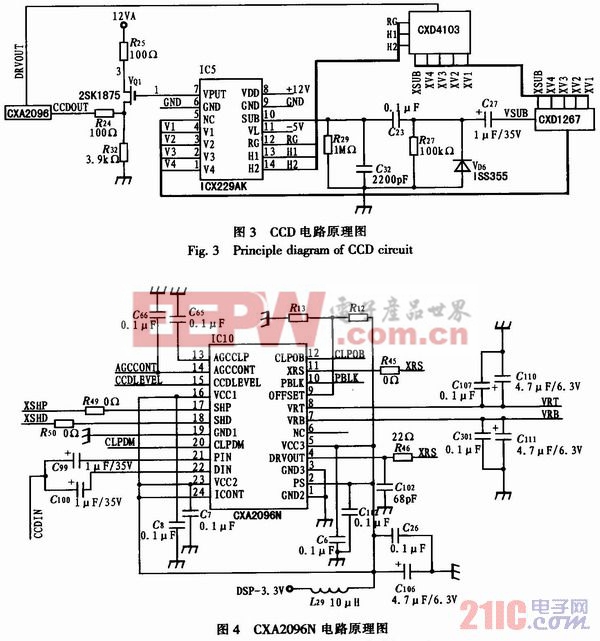

CCD周边电路设计如图3所示。ICX229AK为1/4英寸PAL补色图像传感器,其有效分辨率为PAL制752(H)x582(V),工作电压为12 V,采用14引脚DIP封装;采用超HAD技术,具有很高的灵敏度并能获得高饱和度的视频信号;具有画质细腻、色彩鲜艳、信噪比高等优点。

该CCD采用12 V和-5 V电源供电,DSP时序发生器同时发出行、场时序驱动信号,场驱动信号通过CXDl267进行放大整合后生成供给CCD的场时序驱动信号V1、V2、 V3、V4,与DSP发出的行信号H1和H2同时送到CCD,使其开始正常工作,采集到的电信号经过场效应管2SKl875放大,得到模拟输出信号 CCDOUT,该信号送至采样电路CXA2096。

评论