基于FPGA和USB 2.0的高速CCD声光信号采集系统

在现代通信和雷达领域中,宽带、高增益、实时并行处理是现代接收机的重要标志。因而,这种具有高速并行处理能力和特有的大带宽性能的声光处理系统具有巨大的潜在优势。以声光器件为基础的接收机除了具有宽带、高增益、实时并行处理等特点外,还具有容量大,体积小,功耗低等优点。因而,采用声光信号处理技术解决带宽、高增益和实时并行处理问题具有重要意义,声光信号的采集系统的设计是整个声光系统关键之一。这里设计了一个基于FPGA和USB 2.0的高速CCD声光信号采集系统,为声光信号采集提供了硬件平台。

1 系统概述

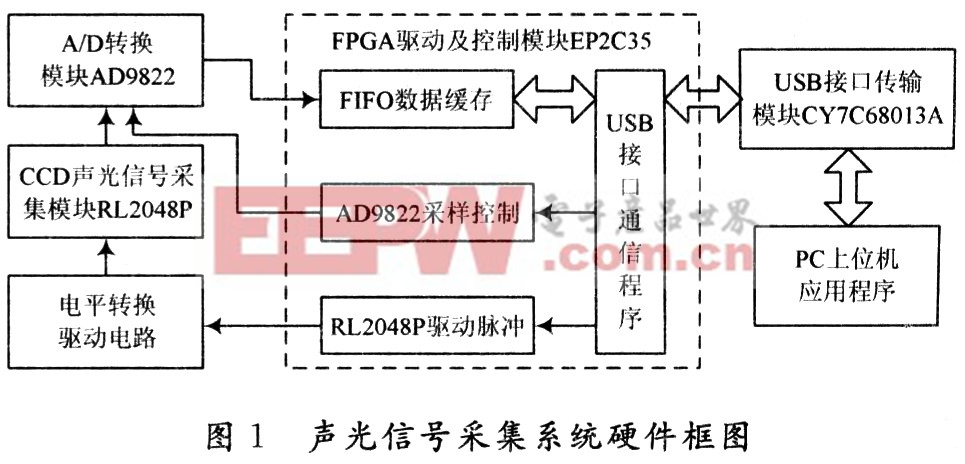

声光信号采集系统框图如图1所示。系统主要由CCD声光信号采集模块、A/D转换模块、FPGA驱动和控制模块及USB接口传输模块四部分组成。

系统上电后,USB设备按照上位机的命令完成对。FPGA数据采集参数的初始化设置及采集控制。RL2048P在驱动时序的严格控制下工作,采集的模拟信号经专用CCD信号处理芯片AD9822的相关双采样及模/数转换后,缓存在EP2C35内部配置的FIFO中,然后判断当FIFO中的数据达到2 048 B时,向USB控制器CY7C68013A中异步写数据,由于USB设置自动IN模式,可以直接把FIFO中数据传输到PC上位机硬盘文件中,因而可完成CCD声光信号的采集、传输及存储。

2 系统各模块设计

系统各模块设计为:

FPGA驱动及控制模块 系统采用Altera公司的CycloneⅡ系列。EP2C35F672C6芯片,具有高性价比及丰富的逻辑资源,可满足系统的要求。有4个PLL,33 216个LE,48 KB存储器资源,可以配置成各种模式的ROM,RAM及。FIFO,35个18×18的专用乘法器。FPGA的主要功能是产生RL2048P驱动时序,控制AD9822采样及对其寄存器实现串行编程,内部配置FIFO缓存数据以及与USB接口通信,并传输数据到上位机中。

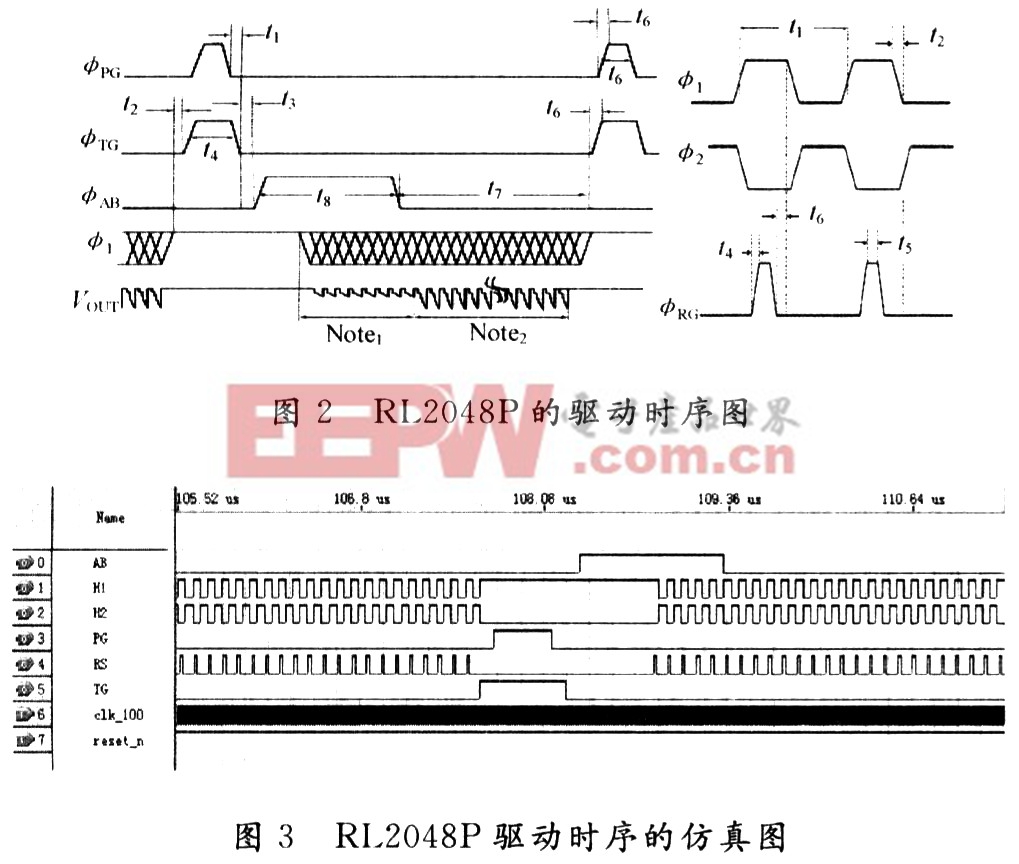

CCD声光信号采集模块 选用PerkinElmer公司的RL2048P线阵CCD。该芯片主要用于高速信号采集,2 048个有效像元,具有高灵敏度、大动态范围、宽光谱范围等特点,最高工作频率为40 MHz,该系统设计为10 MHz。EP2C35的时序驱动输出是3.3 V的LVTTL电平,不能直接驱动RL2048P(多电平要求)。因此,使用DG642和74FCT16244TV芯片完成电平转换,增强驱动能力。图2为RL2048P驱动时序图;图3为使用Verilog HDL编写驱动时序的QuartusⅡ仿真。由比较可见,设计完全能满足时序的严格要求。

A/D转换模块 AD9822是ADI公司的专用CCD信号处理芯片,内部集成CDS,PGA,14位ADC、暗电平自动校准、偏置电压控制以及串行接口等功能,采样速度高达15 MHz。ADCCLK的下降沿输出数据的高8位,ADCCLK的上升沿输出数据的低6位。AD9822采样控制时序及寄存器编程都是由EP2C35实现,与RL2048P输出信号同步,保证采集数据的正确性。采用相关双采样模式可以抑制CCD的复位噪声,本系统设置其寄存器分别为0x0058,0x10C0,0x2000,0x50FF。

USB接口传输模块 USB 2.0协议的传输速度高达480 Mb/s,且具有接口简单及误码率低等优点,能够满足该系统高速传输的需要。选用Cypress公司的新一代低功耗CY7C68013A芯片,与之相应的开发包和开发文档较齐全,缩短了开发周期,降低了开发难度。为了保证数据传输的速度,CY7C68013A工作于SlaveFIFO模式,不需要EZ-USB FX2LP的CPU干预,即可完成与FPGA的数据传输。EP2C35与CY7C68013A的通信采用了Slave FIFO模式下的异步方式,向大端点EP6写数据,配置其为512 B四重缓冲区,批量AUTO IN传输模式,每次自动提交512 B数据。图4为EP2C35与CY7C68013A的接口连接。

评论