电力电子装置控制系统的DSP设计方案

在现代高性能电力电子和交流电机控制系统中,DSP已经取代了微控制器成为控制器的核心。其快速强大的运算和处理能力以及并行运行的能力,满足了电力电子装置控制系统对实时性和处理算法复杂性的要求,并为不断发展的新理论和新算法的应用奠定了技术基础。

C240x系列DSP是面向数字控制系统的新一代数字信号处理器。该控制器集实时处理能力和控制器设计功能于一身,为控制系统应用提供了一个理想的解决方案。其内部的哈佛结构使数据空间和程序空间分离,独立的数据总线和程序总线允许程序数据同时操作;专用的硬件乘法器极大提高了运算速度;具有独特的逆寻址方式,能高效地进行快速傅里叶变换运算;指令系统采用流水线操作,减小了指令周期;采用内存映射方式管理I/0,能灵活方便地扩充外围电路。

1 主电路硬件设计

1.1 系统总体设计

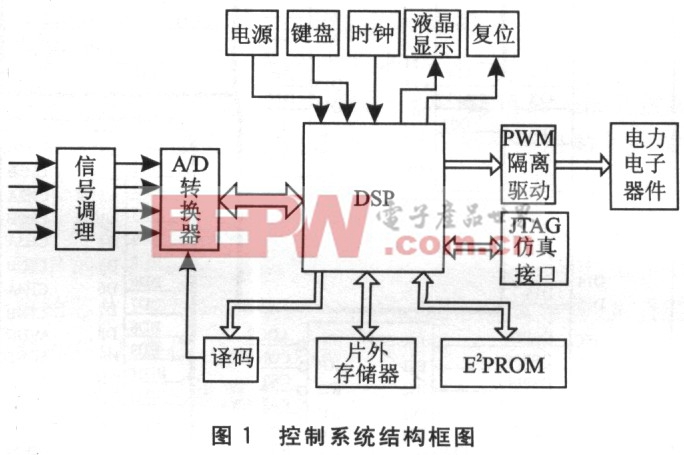

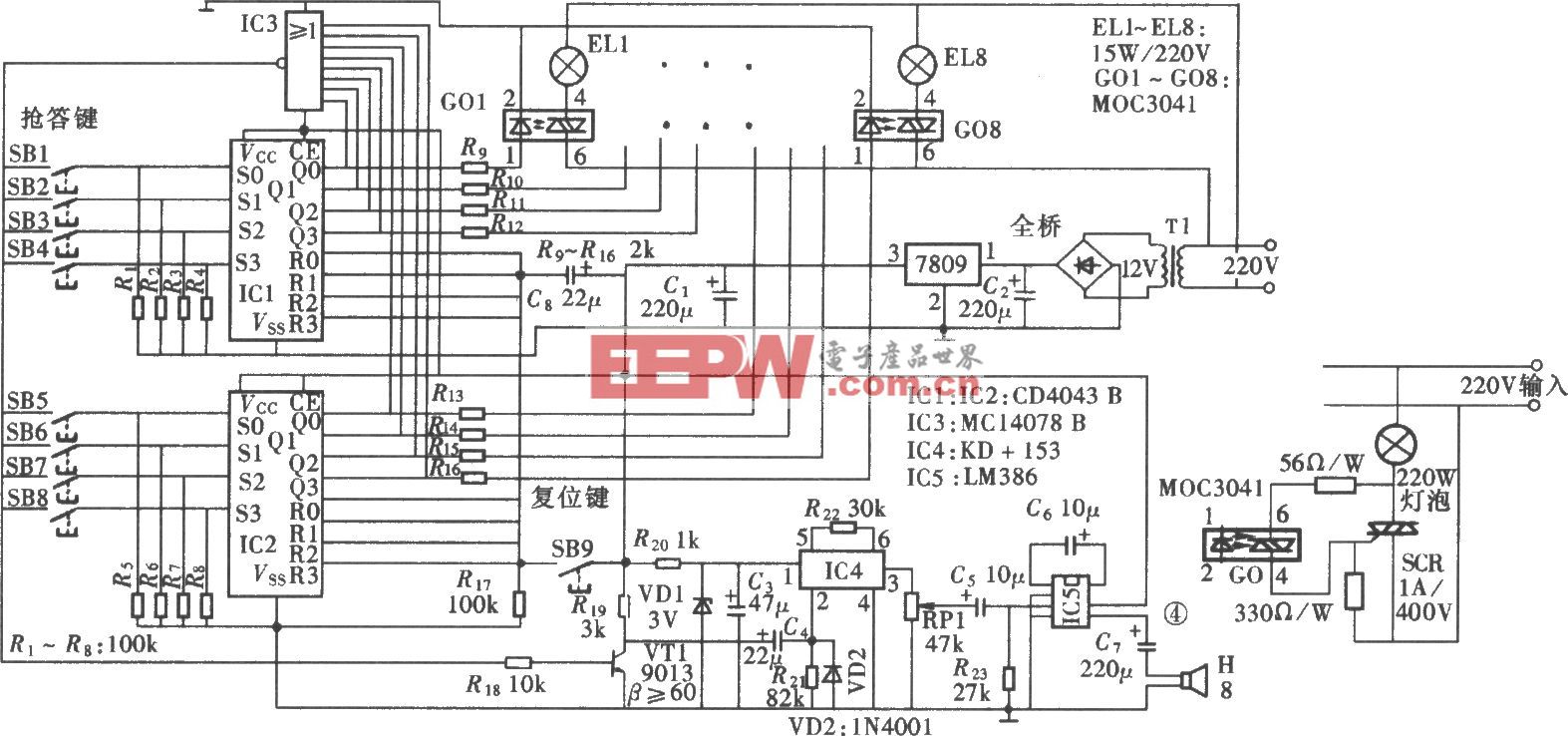

一般电力电子装置控制系统的总体结构如图1所示。详细介绍各单元的功能与硬件电路。

1.2电平转换

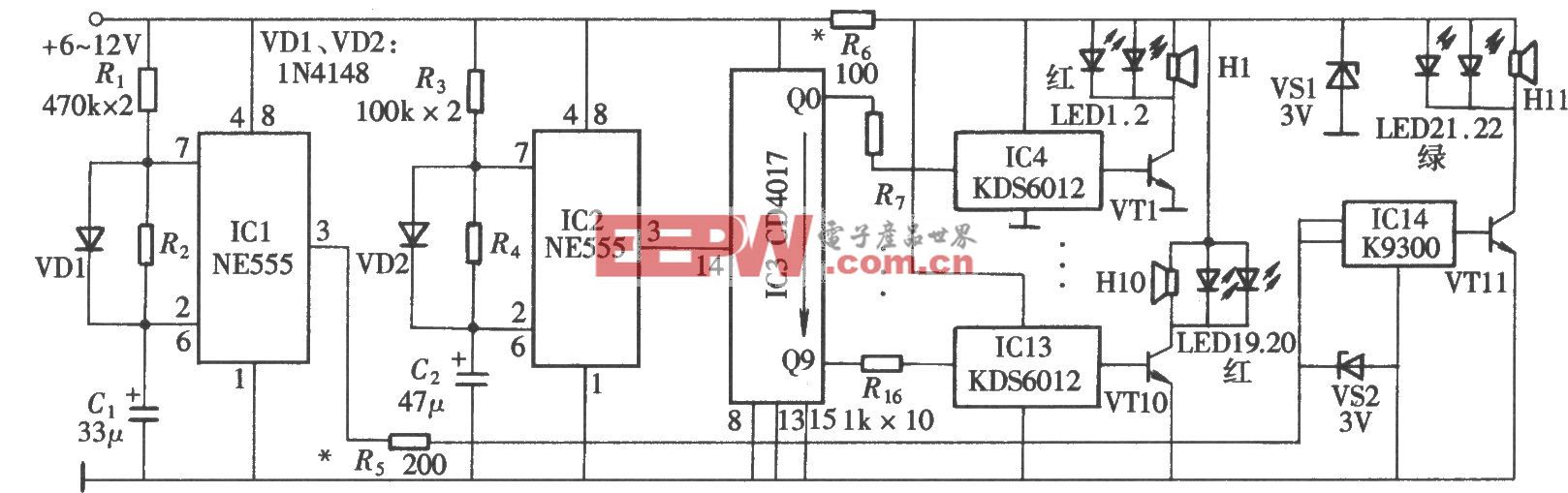

TMS320LF2407a(以下简称2407a)采用3.3V电,减小了芯片功耗;但常用直流电源为5V,因此必须考虑电平转换问题。一种方法是直接采用可调直流电源获得3.3V电压,但这样很难保证电源电压的稳定性,影响DSP的正常运行。另一种方法是采用专门的电源芯片,将5 V电压降为3.3 v。TPS76833、TPS76HD318、MAX604为常用的电平转换芯片。图2为采用MAX604实现电子转换的电路。并联于电源与地之间的电容起稳压作用。

1.3 时 钟

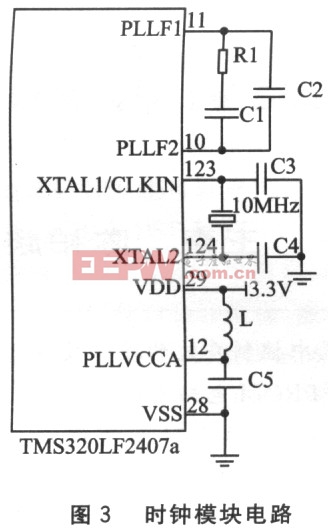

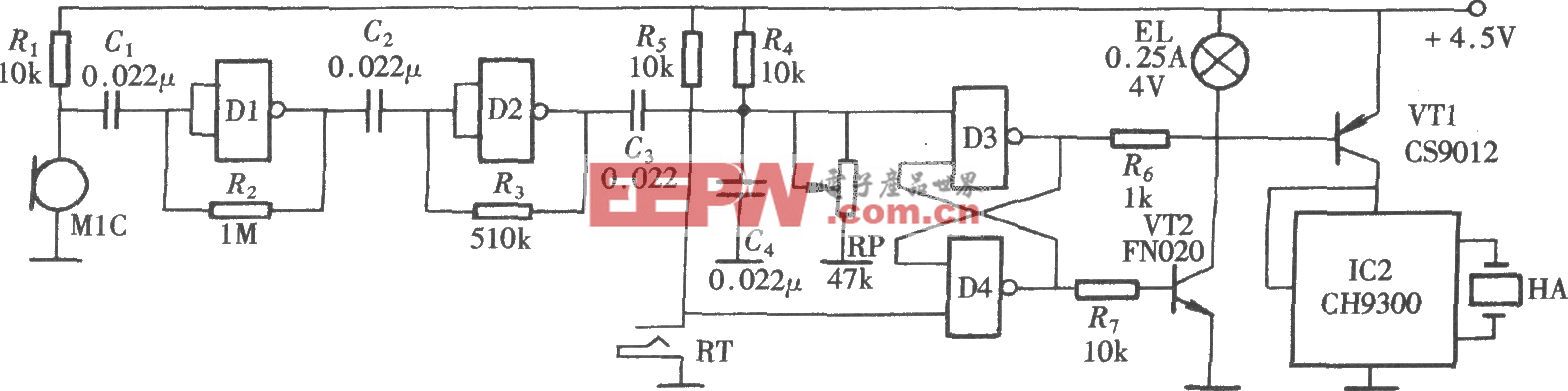

与一般微处理器不同,C240x系列DSP利用挂接在片内外设总线上的锁相环时钟模块(PLL)合成系统需要的各种时钟信号(CPU时钟、系统时钟、模拟时钟和看门狗时钟)。外部时钟信号经PLL倍频后合成系统时钟频率。如图3所示,外部时钟信号由lO MHz晶振提供,通过系统控制和状态寄存器(SCSR1)设置4倍频因子后,2407a DSP以最大时钟频率(40MHz)工作。通过检查DSP时钟输出引脚(CLK0UT)的频率,可以判断DSP芯片是否已开始正常工作。PLL模块使用外部滤波器回路来抑制信号抖动和电磁干扰。滤波器回路由PLL接在滤波器输入引脚PLLF和PLLF2之间的电阻Rl和电容Cl、C2组成。电容Cl、C2必须为无极性电容。在不同的振荡器频率下,R1、Cl、C2的取值不同,常用的参数组合如表l所列。PLL模块的电源引脚PLLVCCA分别通过磁珠和0.1μF的电容与数字电源引脚VDD和数字地引脚VSS连接,构成低通滤波电路,保证时钟模块的可靠供电。

1.4 片外存储器

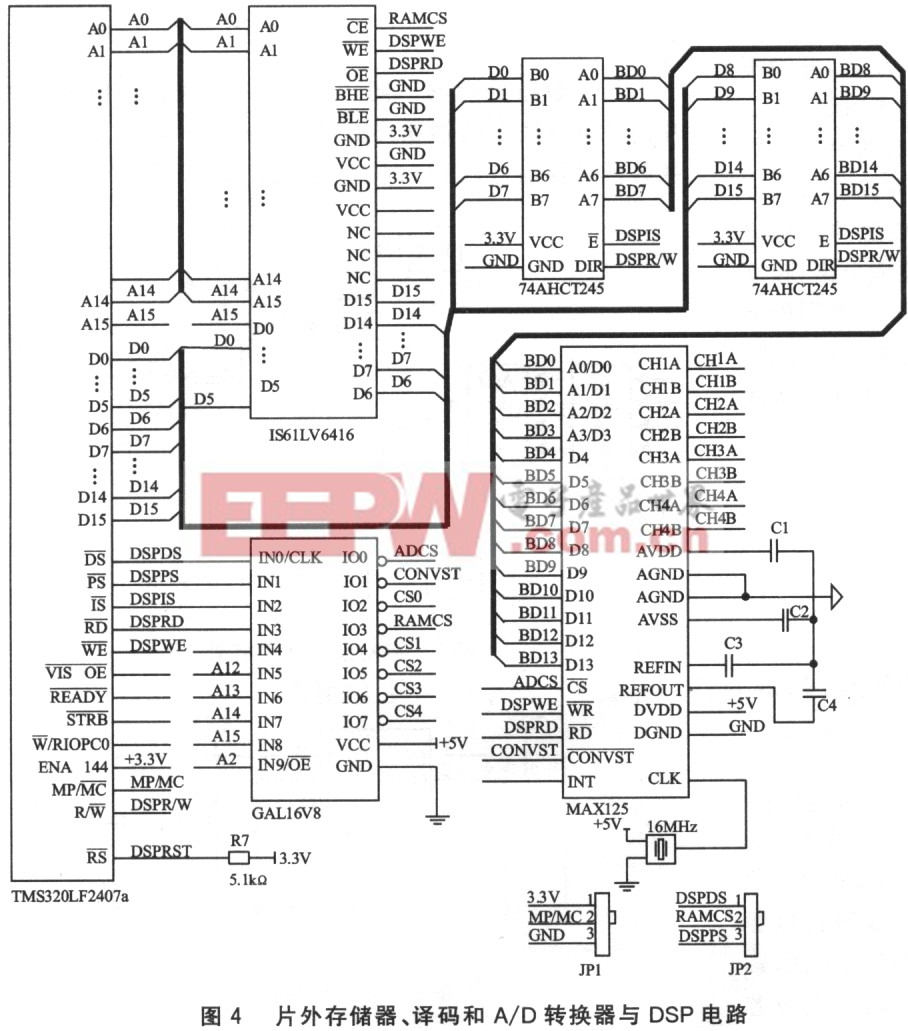

2407aDSP可以访问的程序存储空间为64K字,根据MP/MC引脚的电子决定其配置方式。当MP/MC为低电平时,片内Flash存储空间使能,地址范围是0000h~7FFFFh,8000h~FFFFh的地址留给外部程序存储器。当MP/MC为高电平时,片内Flash被禁止,64 K字存储空间全部位于外部程序存储器中,即只能从片外存储器中读取数据,使得仿真调试时通过仿真器对程序修改比较容易。2407a DSP有64K的16位数据存储器空间,32 K字的内部存储器地址范围是0000h~7FFFh,包括存储器映射寄存器、DARAM和外设映射寄存器。另外,地址范围是8000h~FFFPh的32 K字留给外部数据存储器空间。片外存储器的选择主要考虑电压、容量、速度等指标。本文采用工作电压3.3 V,容量64K×16位,访问时间15 ns的高速静态RAM,IS6lLV6416-15T作为片外存储器。如图4所示,片外存储器的数据、地址线分别与DSP对应相连;输出使能引脚OE和输入使能引脚WE分别与DSP的读选通DSPRD相连。仿真调试时,用跳线把片选引脚DSPWE与DSP的程序空间选通引脚CE相连,当外部程序存储器用。程序烧写到片内Flash后,把片选引脚CE与DSP的数据空间选通引脚DSPDS相连,当外部数据存储器用。

评论