TMS320F206与CPU卡通信协议的优化

1 硬件电路

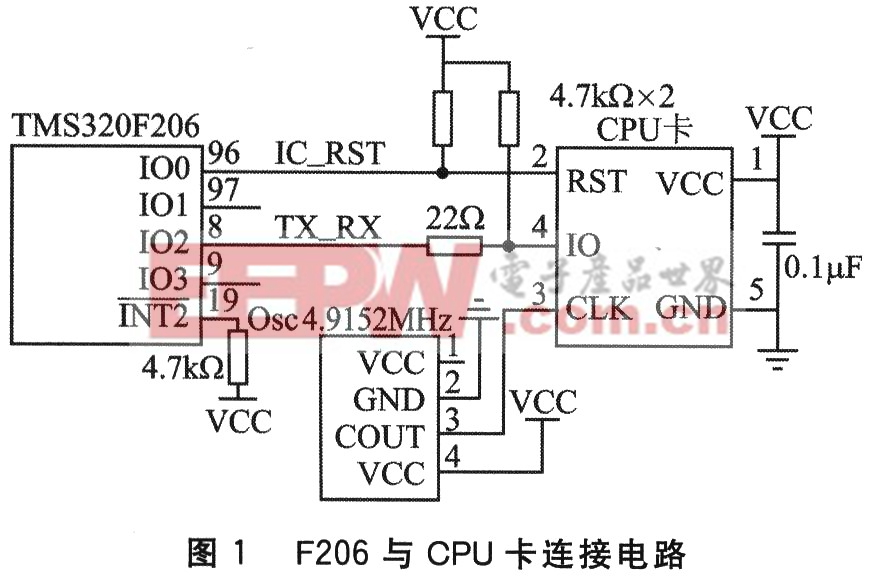

TMS320F206(简称F206)有1个通用输入引脚BIOS和1个通用输出引脚XF,此外还有IO0、IO1、IO2和IO3引脚,分别对应I/O状态寄存器的IO0~IO3。这4个引脚通过异步串行口寄存器(ASPCR)和I/O状态寄存器(IOSR)实现软件可控,可被单独配置成输入或输出。本文中使用IO0作为CPU卡(江苏意源公司iCos/Mil v1.0)的复位引脚,IO2作为CPU卡的I/O(输入/输出)引脚,电路图如图1所示。

2 软件实现

异步串行通信,传输协议bit流为:1位宽的低电平为起始位,8位宽的数据位,1位校验位,以及1位高电平的停止位。软件实现时,通过配置异步串行口寄存器(AS-PCR)和I/O状态寄存器(IOSR),并使用定时器功能,完成F206与CPU卡之间数据的发送与接收。

2.1 数据发送

F206发送数据时,将IO2配置成输出状态,然后启动定时器,按照设置的波特率,分别将发送的数据按字节(8位)加上起始位、校验位和停止位发送给CPU卡的IO2口。

评论