直序扩频的研究与FPGA实现

摘要 直接序列扩频通信系统以强抗噪声、低截获性和多址通信等特点,在军事及民用移动通信网络中得到广泛应用。文中对直序扩频的FPGA实现技术进行了研究。以QuartusII为开发工具,建立了一个初步的直接序列扩频通信系统。设计了发射模块和接收模块,发射模块包括PN码产生器、扩频调制器、接收模块包括匹配滤波器和解扩器;给出了上述模块的实现电路及仿真结果。

关键词 直序扩频;FPGA;PN码;匹配滤波器

扩频通信是现代通信系统中的一种独特的通信方式,其拥有较强的抗干扰、抗多径性能以及频谱利用率高、多址通信等诸多优点。直接序列扩频被许多现存的和未来的蜂窝通信系统采用,并广泛应用在军事通信网络与系统中。

随着微电子制造工艺的发展,可编程逻辑器件取得了长足的进步。可以完成超大规模的复杂组合逻辑与时序逻辑的现场可编程逻辑器件(FPGA),在电子系统的设计中得到越来越广泛的应用。

以Quartus II软件为开发工具,利用FPGA实现了一个基带直接序列扩频通信系统,其包括发送模块和接收模块两部分。

1 直序扩频通信系统的基本原理

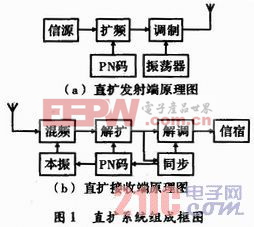

直接序列扩展频谱系统(Direct Sequece Spread Spectrum Communication Systems,DS-SS),简称直扩系统,是用待传输的信息信号与高速率的伪随机码波形相乘,去调制射频信号的某个参量,来扩展传输信号的带宽。原理如图1所示。

在发信机端,待传输的数据信号与伪随机码波形相乘形成的复合码对载波进行调制,然后由天线发射。在收信机端,要产生一个和发信机中的伪随机码同步的本地参考伪随机码,对接收信号进行解扩。解扩后的信号送到解调器解调,恢复出传送的信息。

2 直序扩频通信系统发送模块的设计与实现

发射子系统主要包括信息码的输入模块、扩频伪随机码的产生模块及扩频模块。

2.1 信息码输入模块

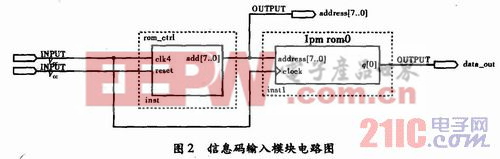

该模块提供系统仿真及调试用的输入数据源,数据固化在ROM中。设置为200字长、1位宽。设计ROM的地址控制模块,以给定的时钟驱动一个计数器来循环产生地址信息,使得ROM中存储的待发射信息循环不断的输出。

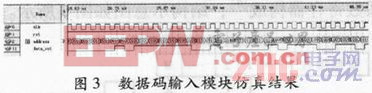

利用Verilog语言设计地址控制模块,利用QuartusⅡ提供的LPM定制ROM模块,用原理图设计生成顶层实体,可得如图2所示的电路及图3所示仿真结果。

从结果可以看出,在时钟控制下,地址输入端循环产生地址信息使ROM中的数据循环输出。

评论