基于FPGA的嵌入式串行千兆以太网设计

摘要:本设计以Xilinx FPGA为棱心芯片,利用内嵌硬核处理器PowerPC、嵌入式操作系统Xilkernel和LwIP协议功能函数,完成嵌入式串行千兆以太网系统的设计。本设计能够满足以太网通信对高速数据传输的要求,同时在电路设计时,具有PCB布线简单以及信号完整性好等优点。

关键词:千兆以太网;FPGA;SGMII;PowerPCA40

引言

随着通信技术的发展,千兆以太网因在传输中具备高带宽和高速率的特点,成为高速传输设备的首选。基于Xilinx FPGA的嵌入式系统设计整合了一系列的知识产权(IP)核使其功能强大,从而使得利用FPGA进行嵌入式串行千兆以太网开发成为可能。

本设计使用Xilinx公司65 tim工艺级别的Virtex-5FXT系列芯片,满足嵌入式系统设计所应具备的高性能、高密度、低功耗和低成本的要求。V5 Hard TEMAC模块提供了专用的以太网功能,并通过FPGA内部高速串行收发器GTX和Marvell公司的88E1111物理层接口芯片相连,完成串行千兆以太网的接口功能。物理层接口芯片支持MII、GMII、RGMII和SGMII四种以太网接口模式。相对GMII接口而言,SGMII接口的I/O端口数目少,便于PCB布线,并且数据信号以差分对的形式出现,有利于保证信号完整性。

本文将FPGA内嵌PowerPC硬核处理器、Xilinx精简嵌入式操作系统Xilkernel,以及相应的外设IP Core相结合,完成嵌入式串行千兆以太网的设计。

1 总体设计

系统硬件平台中选用Xilinx公司的Virtex-5 FX70t作为主控芯片,它集成了PowerPCA40处理器模块和高速RocketIO GTX收发器。

外部存储器采用Mcron公司的128M×16位DDRSDRAM芯片MT47H128M16HG-31T,为程序运行提供空间。

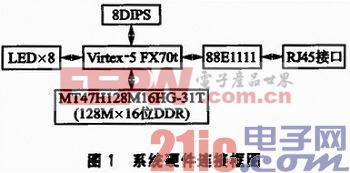

在网络芯片方面有两种方案可供选择,即单物理层芯片方案和物理层加MAC层集成于同一芯片方案。基于易于控制方面的考虑,采用Marv ell公司的88E1111单物理层接口芯片作为解决方案,该芯片支持10BASE-T、100BASE-TX和1000BASE-T以太网协议。本系统硬件由Virtex-5 FX 70t芯片、88E1111 PHY芯片、DDRII芯片、8个拨码开关(8DIPS)、8个LED灯和RJ45接口构成,其连接框图如图1所示。

串行千兆以太网设计中,需使用FPGA内部RoeketIO GTX收发器完成SGMII链路的建立。RoeketIOGTX是集成在Virtex-5 FX70t芯片中灵活的、功能可配置的千兆位级串行收发器,支持750 Mbps~6.5 Gbps的数据传输速率,满足千兆以太网系统设计中数据传输速率的要求。本设计通过在FPGA中例化EMAC硬核,并将相应的FPGA端口和外部PHY芯片88E1111相连完成SGMII链路的建立。SGMII接口使用全双工模式,有收发两个独立的通道,每个通道使用一对差分信号线,采用无时钟信号模式,RoeketIO GTX收发器从串行数据中恢复时钟用于差分数据的发送与接收。

SGMII接口实现框图如图2所示。

fpga相关文章:fpga是什么

评论