ARM中断处理的安全性与高效性研究

摘要 重点分析了ARM处理器的多种中断处理,包括普通中断处理、任务切换中断处理、可重入中断处理和基于优先级的可重入性中断处理的上下文保存技术,并给出了程序予以实现。对普通的前后台系统和带OS的嵌入式系统都有实用价值。

关键词 ARM中断 高效安全 上下文保存

引 言

在嵌入式系统中常用的RISC处理器是ARM核,它具有体积小、功耗低、成本低、性价比高的特点。然而,不管是哪种型号的ARM处理器,也无论该嵌入式系统中是否有操作系统,中断处理,特别是IRQ中断,始终是必须的,而中断处理的核心问题是上下文的保存。能否安全而又高效地保存上下文,将影响一个嵌入式系统的性能与稳定。笔者对ARM处理器的普通中断处理、任务切换中断处理、可重人中断处理和基于优先级的可重人性中断处理的上下文保存技术进行分析与总结。为保证理论的正确性,核心的程序代码都经过了实验的检测。

1 系统中断处理简介

ARM处理器的中断主要有两种:IRQ普通中断和FIQ快速中断。快速中断本质上与普通中断没有太大的差别,它们在处理机制上有许多相同的地方。IRQ中断是最频繁的也是最为影响系统性能的,所以对它的研究与处理也就最有价值。

下面简要地介绍一下IRQ异常发生时ARM处理器的工作过程。在IRQ中断发生时,ARM处理器的硬件会自动执行以下工作:

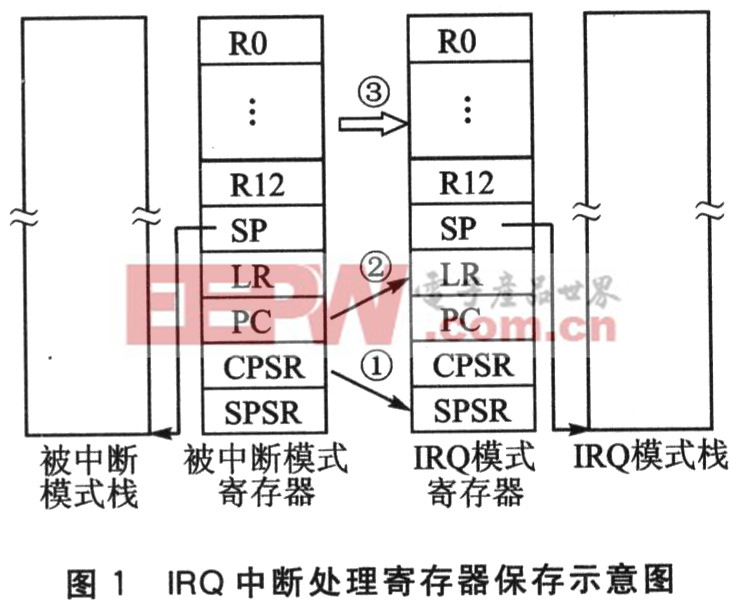

①将被中断任务模式的CPSR值保存到IRQ模式中的SPSR寄存器中;

②将被中断任务模式的PC值保存到IRQ模式中的LR寄存器中;

③将模式自动切换到IRQ模式,并将CPSR中的bit7位置1禁止后继IRQ中断的发生;

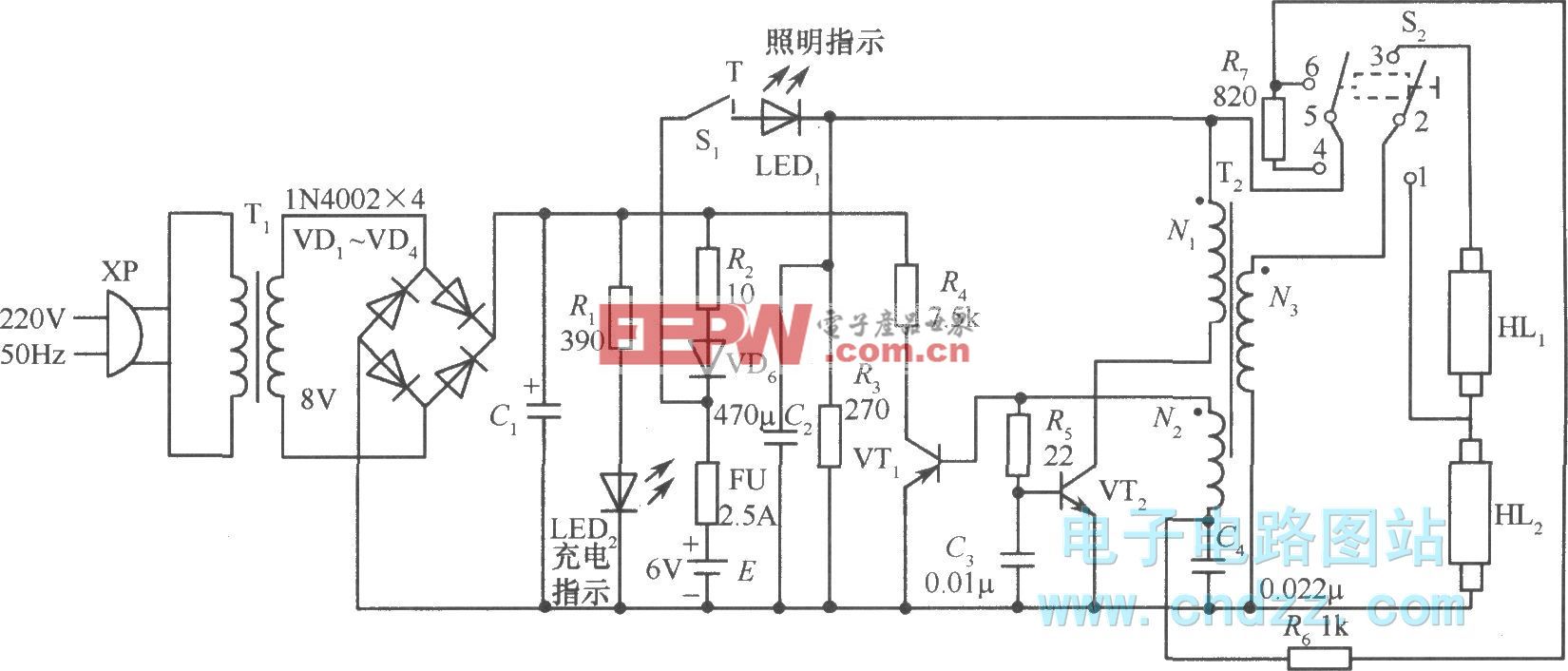

④PC被赋予0xl8的地址值,程序将从0xl8片开始执行。结合图1,可以更好地理解ARM中断处理机制的工作过程。

2 普通中断处理

有些ARM嵌入式系统可能对中断的要求比较低,即发生中断后首先查询相应的中断源,然后进行中断服务,最后从中断服务程序中返回到被中断处继续运行程序。如何在这种简单应用中保证安全又高效地处理中断呢?“安全”就意味着中断发生时上下文被完好保存不被破坏,“高效”就是说保存尽可能少的寄存器(当然是建立在安全的基础上的)。由图1可知,在普通中断处理中,中断服务就可以在IRQ模式中运行。根据ATPCS的调用规则,在子程序调用中ARM编译器保存了R4~R11寄存器,因此就没有必要再次保存。那么剩下的寄存器就必须予以保存,防止从中断服务程序返回后被破坏。可以用汇编语言和C语言书写处理代码。

评论