基于中档FPGA多相滤波器的设计实现

在现代电子系统中,到处都可以看到数字信号处理( DSP )的应用,从MP3播放器、数码相机到手机。DSP设计人员的工具箱的支柱之一是有限脉冲响应( FIR )滤波器。FIR滤波器越长(有大量的抽头),滤波器的响应越好。然而这里有折衷的情况,由于大量的抽头增加了对逻辑的需求、增加了计算的复杂性,增加了功耗,以及可能引起饱和/溢出。

本文引用地址:https://www.eepw.com.cn/article/151434.htm多相技术可以用于实现滤波器,拥有与传统FIR滤波器可比的结果,而且使用了较少的逻辑、需要较少的计算资源、更低的功耗,并减少了可能的饱和/溢出。可用如今新型的小规模、中档的FPGA,如LatticeECP3 来实现这些滤波器。

基本概念

进入DSP世界可能会有些令人生畏,因此,让我们首先介绍一些简单的概念。对于数字系统,如音频,视频和无线领域,形成信号的结果是与采样率相关的。举例来说,以48 kHz(即每秒48000个样本)对专业音频信号进行采样。相比之下,消费者的CD播放机则使用44.1 kHz的采样率。

多速率系统

多速率系统使用多个采样速率。在某些情况下,运行于某个速率的系统的一部分需要一个原来以另外某个速率采样的信号(转换专业音频到消费者的CD音频就是一个例子)。在这种情况下,原始信号的速率必须根据需要增加或减少。

或者针对特定的用途,也可能以比实际需要更高的速率对原来的数据进行了采样。因此,降低采样率,然后运行所得到的数据就可以大幅度降低数据吞吐量的要求,降低对存储器的要求,提高处理效率并降低功耗。

向下采样和抽取

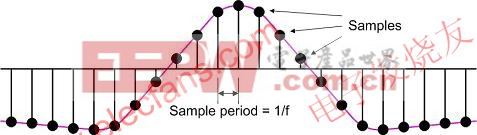

让我们首先考虑降低采样率的问题。假设我们有一个信号,原来以我们称之为fHz的某一频率进行采样,如如图1所示。

图1 用f Hz采样率对原始信号采样

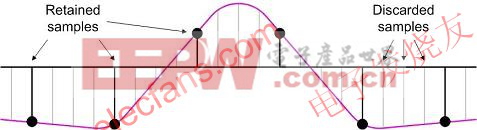

现在假设我们要降低采样率至原来频率的1/4。达到此目的一个方法来就是简单地扔掉每四个原始采样中的三个,如图2所示。

图2 用1/4 f Hz采样率得到新的信号

在数字信号处理中, “混叠现象”是指采样时造成不同的连续信号彼此难以区分的情况,它们互相“混叠”。 混叠现象也称为失真,或赝品,即源于采样重构的信号不同于原来的连续信号。

如果我们丢弃了如上文所讨论的一些样本,由此得到的信号会含有混叠现象的赝品。作为一个简单的例子,考虑一个音频信号,可能含有人耳听不见的高频分量的乐曲。如果我们以过低的速率对这个信号采样(当我们丢弃一些样本时,实际上是我们正在做的事情),然后用数字模拟转换器重构这个乐曲,我们可以听到欠采样高频分量的低频混叠。

为了避免这种情况,常见的做法是在丢弃不想要的样本之前,用低通滤波器去除不要的高频,如图3所示。

图3 在丢弃任何样本前对这个信号进行滤波

一般而言, “向下采样”只是指丢弃样本的处理而不执行滤波的操作。相比之下, “抽取”指的是降低采样率的整个过程,即执行滤波操作,然后丢弃样本。实际上, “向下采样” 、“下变频”和“抽取”往往交替使用。

“抽取因子”是指输入采样率与输出采样率之比。通常用字母M来表示。在上面的例子中,输入速率是输出速率的4倍,所以M=4。

向上采样和内插

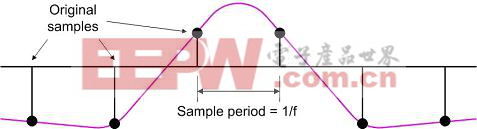

现在考虑的情况是,我们希望提高采样率。这样做的原因是为了使系统的另一部分与信号运行在更高的采样速率。假设我们从一个信号开始,即原来以我们称为fHz的某个频率进行采样的信号,如图4所示。

图4 采样率为f Hz的原始信号

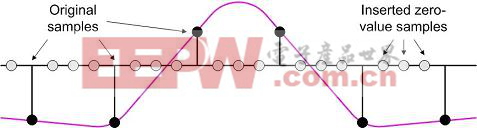

现在假设我们要增加采样率为原来频率的4倍。我们开始在原始样本之间插入零值样本,以提高采样率,如图5所示。

图5 用零值样本对原始信号进行扩充

评论