嵌入式非易失性存储器在SoC物理设计中的应用

摘要:嵌入式非易失性存储器以其同时具备数据可更改性及掉电保存性而已被越来越广泛的应用于SoC物理设计。文中结合一款电力网控制芯片R36的实际设计案例,分析了该器件的应用特点,并从用途、性能、容量选择等方面说明了通过非易失性存储器对降低芯片成本、提高速度及可靠性应用方法。

关键词:非易失性存储器;电可擦除只读存储器;闪存;片上系统

0 引言

非易失性存储器是指在系统关闭或无电源供应时仍能保持数据信息的存储器,常见的有EPROM、EEPROM、Flash-EEPROM等。由于其同时具备数据更改性及数据保存性,NVM在系统设计中被大量应用于数据及程序的存储,并逐步替代部分有断电保存需要的RAM,甚至取代部分硬盘功能,如固态硬盘(SSD)。传统的系统解决方案采用外挂片外NVM芯片,这种方法会使系统复杂度提高。而随着嵌入式NVM技术的发展,将NVM与系统其它电路集成在同一块芯片中,已成为SoC系统设计的新趋势。相对于传统的片外NVM方案,嵌入式NVM具有更高的数据交换速度和更高的可靠性。然而,在SoC芯片的物理设计中,嵌入式NVM也面临工艺兼容、功耗及成本控制等新的问题。为此,本文以一款电力网控制芯片R36的物理设计为例,讨论了嵌入式NVM在实际应用中需要注意的问题,并给出了解决方案。

1 嵌入式NVM简介

1.1 嵌入式NVM的工作原理

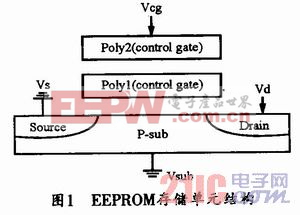

大部分NVM的工作原理都是以基本的EEPROM为存储单元。与普通MOS管相比,EEPROM存储单元多了一层多晶硅浮栅,图1所示是EEPROM的存储单元结构,该存储单元的基本操作为擦1、写0及读取。擦1时,Vcg为12 V,Vd为6 V,漏栅之间的电场使漏端电子穿越氧化层势垒而到达浮栅并存储,该过程称为热电子注入,这样,即使Vcg高压除去后,浮栅上的电荷也能保存很长时间;写0时,Vcg为-12 V,Vd为6 V,漏栅之间的电场给浮栅上的电子提供释放到P-sub的通路,称为FN隧道效应,此后,浮栅电荷被释放。

嵌入式NVM首先要解决的问题就是与芯片其它电路工艺(logic)的兼容。依据芯片中NVM所占面积的比重,嵌入式NVM通常有两种兼容方案。一是当NVM比重大于其它逻辑时,把logic工艺映射成NVM工艺,这是最方便的做法;二是当NVM容量较小(32 Mbits)时,为了节约产品开发时间,通常把NVM做成可复用的IP,然后映射成logic工艺。

1.2 常见的嵌入式NVM

目前常见的嵌入式NVM有EEPROM和flashEEPROM(简称flash)两大类,EEPROM每个存储单元都配有一个门控开关,故可实现单元独立擦操作;而flash存储单元没有独立的门控开关,通常以page为单位进行擦操作,因此,相同容量的EEPROM面积会大于flash,但单个单元擦写时间则小于flash,且擦写时不影响其他单元的状态,同时,使用寿命较flash有很大的优势。常见的flash也因其架构不同,可分为NORflash和NANDflash两类,NAND flash架构更为紧凑,成本/容量比更优,但目前嵌入式技术相对没有NOR成熟。

评论