ST-BUS总线接口模块的Verilog HDL设计

ST-BUS是广泛应用于E1通信设备内部的一种模块间通信总线。结合某专用通信系统E1接口转换板的设计,本文对ST-BUS总线进行了介绍,讨论了ST-BUS总线接口收发模块的设计方法,给出了Verilog HDL实现和模块的时序仿真图。

关键词:ST-BUS;Verilog HDL;接口模块;E1;CPLD

引言

随着数字技术的迅速发展,现代通信系统已成为一个庞大的综合化数字网络。电信核心网络除了提供传统电话服务外,还为其它专用通信(比如警用集群通信等)提供中继服务。电信系统一般从交换机引出E1信号线路以供其它专用通信系统接入。为了满足电信网的接入规范,E1终端设备内部常采用一种被称为ST-BUS的总线来对需要接入通信网的各路用户数据进行排队,以便统一与E1信号进行转换,充分利用E1线路资源。由于批量生产的接口芯片都是针对某些特定标准接口而设计,无法满足E1通信的特殊需要。为满足多种特殊接口与电信线路间进行数据交换的需要,增加系统可重配置的灵活性,本文在所涉及项目中的E1接口转换板的设计中采用了可编程器件实现了多种特殊接口的混合接入。为了简化问题,文中主要介绍ST-BUS总线接口收发模块的Verilog HDL设计。

ST-BUS基本原理

ST-BUS(Serial Telecom BUS,串行通信总线)是卓联半导体公司根据电信应用的需要而定义的一种重要的通信设备内部总线通信协议,它可以将多路信息(包括音频、视频、控制信息以及其它数据等)进行复接或解复接,以便统一进行信号转换,实现本地设备与电信E1线路间的数据交换。随着通信系统越来越复杂,电信设备常有局部部件的淘汰或者更新换代。为了提高设备兼容性也便于系统升级,电信设备广泛采取了模块化设计方法,而ST-BUS就是将各功能模块连接起来协同工作的一种总线标准。所以,不论模块的功能和外部接口怎样,只要具备ST-BUS总线接口,都可以方便地嵌入到特定的通信系统中。

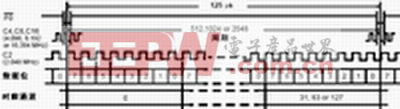

根据卓联对ST-BUS的信号及时序规范所作的定义,ST-BUS是一种传输数字信息的高速同步串行通信总线,总线接口所需信号有帧同步信号、位时钟信号和串行数据信号。帧同步信号主要有类型0和类型1两种:类型0的同步脉冲仅出现在帧的开头,如图1所示,总线上各部件将之作为重要参考信号并由此决定何时开始接收或发送数据流;类型1的同步脉冲需要维持一个完整的时隙周期(即8个位时钟周期),在此期间部件也要接收或发送信息数据,这种同步方式较少应用。ST-BUS定义了4种标准时钟频率,即16.384MHz、8.192MHz、4.096MHz和2.048MHz,其中每一种时钟频率均可作为部件的内部时钟,不过任意时刻只能选择其一,自适应系统在设计时采用了自动选择模式。除频率2.048MHz外,其它时钟频率总是数据速率的两倍,即支持最大数据速率为8.192Mbps。如果ST-BUS数据速率为2.048Mbps,那么时钟可以是2.048MHz或4.096MHz。由图1可知,一个完整ST-BUS的帧周期为125ms,而每帧又根据数据速率分为几种不同的时隙总数。但是,为了与E1信号的时隙相对应,E1终端子系统常采用每帧32时隙的信号方式。

ST-BUS收发模块设计与仿真

为了实现ST-BUS总线与各种不同(总线)接口之间的可靠数据传输,下面讨论同步模式下ST-BUS接口模块的设计,并在部分Verilog HDL描述中以注解方式进行详细说明。根据ST-BUS总线协议,ST-BUS接口模块可大致分为接收模块、发送模块和控制模块(含数据交换)三部分,分别完成ST-BUS总线数据的接收、发送和控制(包括与其它接口单元进行数据交换)等功能。要实现某种特定接口(如RS-232等)与ST-BUS总线之间的数据通信,则需要将该接口单元的I/O信号及控制信号接到ST-BUS接口的控制模块,通过控制模块来控制收发时序以及在ST-BUS中所占用的时隙位置及数目,而在实际应用中,各路数据对应的时隙位置及数目常通过外部控制接口设置。为简化问题,这里仅讨论ST-BUS接口收发模块设计,且假定时隙设置是固定的。

如图1所示,ST-BUS总线的数据收发遵守以下规则:发送端在时钟C2的上升沿发送,而接收端则在C2的下降沿采数据,且同步脉冲在0时隙开始的第一个C2上升沿处保持低电平。

图1 类型0帧同步ST-BUS总线信号时序

ST-BUS接收模块

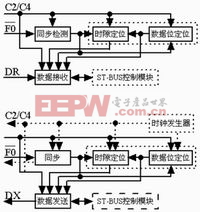

ST-BUS接收模块主要根据控制模块所设置的ST-BUS时隙等参数接收所需时隙的数据,并将接收到的数据送给控制模块,其原理结构框图如图2(a)所示。

图2 ST-BUS收发模块的原理结构框图

根据时钟等信号的提供方式,模块的工作模式常分为主动模式和被动模式两种。由于图2(a)所示的接收模块所需时钟与同步信号均来自外部,因此该模块处于被动模式;相反,如果时钟和同步信号由模块产生,则模块处于主动模式。

被动模式下ST-BUS接收模块的基本工作原理为:上电后,在时钟稳定的情况下,模块首先检测同步信号;在非同步状态下,除同步检测以外的其它部件均不能工作;检测到同步后(即在同步状态下),模块启动时隙定位和数据位定位的计数器工作,此时,模块根据参数设置进行数据接收。另外,图2(a)中的时隙定位和数据位定位在本设计中采用2个计数器实现,也可以合并为单计数器实现。ST-BUS总线接收操作的关键之处在于前一帧的最后一时隙(即31时隙)与当前帧的第一时隙(即0时隙)之间的切换操作,因为需要同时检测同步信号,而一旦同步信号没有检测到,则模块会进入失步状态。接收模块的Verilog HDL实现(信号和常数声明从略,且代码已简化,下同)可以划分为以下三部分。

评论