如何优化嵌入式DSP应用的功耗

采用软硬件技术可以提高电源效率,而使用内置电源管理 API 的 DSP RTOS 更容易实现上述目的。

本文引用地址:https://www.eepw.com.cn/article/150616.htm作者:Scott Gary,德州仪器 (TI)

无线及有线系统设计师均必须重视电源效率问题,尽管双方的出发点不尽相同。

对于移动设备而言,更长的电池使用寿命、更长的通话时间或更长的工作时间都是明显的优势。降低电源要求意味着使用体积更小的电池或选择不同的电池技术,这在一定程度上也缓解了电池发热问题。

对于有线系统而言,设计师可通过减小电源体积、减少冷却需求以及降低风扇噪声来提高电池效率。人们很少会提到这样一个事实:提高电源效率还可节省空间,用以增加能够提高系统性能的组件,尤其是设计小组希望添加一个以上处理器时,这一点非常重要。

设计嵌入式 DSP 处理器或系统功耗要求严格的系统时,采用 DSP 专用技术、操作系统及其支持软件可以降低功耗。超越传统技术的 DSP 或双处理器设计在节约能量方面表现出色。

本文将讨论传统及专门针对 DSP 的功耗优化技术,首先对使用到的术语和原理进行定义与说明。

功耗基础知识

互补金属氧化物半导体 (CMOS) 电路的总功耗是动态功耗与静态功耗之和 [参考资料 3]:

![]()

当门发生逻辑状态转换并产生内部结点充电所需的开关电流以及P 通道及N 通道同时暂态开启引起直通电流时,就会出现动态功耗。通过以下公式可以估算其近似值:

![]()

其中,Cpd 为动态电容,F 为开关频率,Vcc 为电源电压,而 Nsw 为转换的比特数。

另外,电压 (Vcc) 决定着稳定工作状态下的最大开关频率 (F)。

上述关系中包含两个重要概念:

- 动态功耗与开关频率呈线性关系,与电源电压呈二次关系。

- 最大安全开关频率取决于电源电压。

为便于本文讨论,将特定的频率及电压对称为“设定点”。

很显然,降低 CPU 时钟速率将相应成比例地降低动态功耗,由于动态功耗与电源电压成二次关系,在不影响系统性能的前提下,通过降低电压就可能额外大大降低功耗。

不过,对于特定任务集,降低 CPU 时钟速率也会成比例地延长执行该任务集的时间,因此必须仔细分析应用以确保满足其实时需求。

静态功耗主要是由于晶体管漏电流造成的。一般说来,CMOS 电路的静态功耗很低,与其动态功耗相比可以忽略不计。嵌入式应用在不工作期间通常会“闲置”CPU 时钟以减少动态功耗,从而显著降低总体功耗。

而在未来的设计中必须特别关注静态功耗问题,因为更高性能的新型晶体管的漏电流将显著提高 [参考资料 13]。

嵌入式系统常用技术

常用电源管理技术可以分为两类:通过早期硬件设计决策实现或在系统运行时实现。

设计早期的决策对满足性能及功耗至关重要,下面列出了设计中需要考虑的十大要素,其中包括硬件选择、设计策略及架构选择。大多数要素都是嵌入式系统的基本要求,其它要素则需要单独考量。尽管下列决策是在设计早期制定的,但有些仍需在整个设计周期中进行再验证。如下所列:

- 选择低功耗组件

- 分割电压与时钟域;

- 支持电压及时钟缩放功能;

- 启用保持电压门控功能;

- 利用软件中断减少轮询;

- 采用分级存储器模型;

- 降低输出负载;

- 引导时关闭非关键无动力资源;

- 尽量减少活动 PLL 数量;

- 使用时钟分割器快速变换频率。

有关上述列表的详细信息如表 1 所示。

表 1. 通过早期硬件设计决策降低功耗

确定系统架构以后,设计团队需要将注意力转向系统运行时环境。虽然以下列出的仅 14项,但在设计过程中要始终关注其中大部分内容。

- 不需要时则关闭门时钟

- 引导过程中主动关闭不必要的功耗

- 仅在需要时用门向子系统供电

- 激活外设低功耗模式

- 充分利用外设活动检测器

- 使用自动刷新模式

- 通过基准应用确定最小必需频率及电压

- 根据总体活动情况调整 CPU 频率及电压

- 动态调度 CPU 频率及电压以匹配预测工作负载

- 优化代码的执行速度

- 使用低功耗代码序列及数据模型

- 使用代码覆盖技术减少对高速内存的需求

- 更换电源时进入简化性能模式

- 平衡精确度与功耗的关系

老练的设计团队必须至少要从概念上熟悉上述嵌入式系统应用设计要素(其中一项与 DSP电路有关),有关上述列表的详细信息如表 2 所示。

表 2. 通过常用运行时技术降低功耗

实现表 1 及表 2 所述做法及策略并不容易。任何降低功耗的设计都有可能对性能产生负面影响或导致系统不稳定。下表列出了使用基本电源管理技术所面临的主要难题。

表 3. 实际嵌入式系统设计面临的主要难题

DSP RTOS 如何解决难题

大多数老练的嵌入式系统设计师都知道,表 2 中列出的许多技术问题都可以在操作系统中解决,而不必让每个新的设计项目都“从零开始”。

上述最有价值并且得到普遍认可的技术中的一个子集已包括在 RTOS 中,相关技术包括:闲置、关闭活动电源、器件驱动器通知、内存管理、V/F 缩放。由于设计目标不尽相同,将这些技术构建到 RTOS 中需要很多技巧。设计师必须可以选择混合或匹配子集。关键的设计目标就是高效性、灵活性以及操作系统的松耦合。

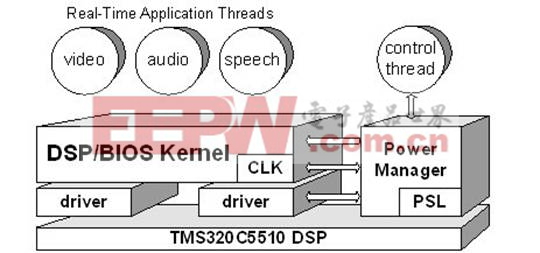

TI 的 DSP/BIOS™ 操作系统的电源管理器 (PWRM) 非常适于用作现有 RTOS 的电源管理模块 [参考资料 4]。尽管以下描述的实施是就特定 DSP/BIOS 而言的,但其概念可简单地运用其他操作系统,甚至用于无操作系统的应用环境。

电源管理器的要求

电源管理器实施的关键要求如下:

- 管理决策必须由应用触发,而不是操作系统触发;

- 电源管理活动应当针对大部分应用代码透明;

- 电源管理器必须支持电压与频率 (V/F) 缩放,并充分利用芯片空闲与睡眠模式;

- 电源管理器必须在应用代码、驱动器以及操作系统本身范围内协调电源事件处理,并在发生特定事件时向客户端发出通知;

- 电源管理特性必须在任何线程环境中可用,并且还必须对特定客户端的多个实例可用(如一个器件驱动器的多个实例);

- 在向客户端发出电源事件通知时,电源管理器必须支持事件处理的延迟完成,并在等待延迟客户端的完成信号的同时通知其他客户端;

- 对具有不同功能的不同平台,电源管理器必须是可扩展的和便携性的。

为满足上述的关键要求,可将电源管理器作为 DSP/BIOS 的附属模块被添加,如图 1 所示。

图 1. 电源管理器分区

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论