基于FPGA的电子设计竞赛电路板的设计

引言

本文引用地址:https://www.eepw.com.cn/article/150113.htm全国大学生电子设计竞赛至今已成功举办了八届, 参赛人数越来越多, 竞赛规模越来越大。大学生电子竞赛在培养学生创新能力、促进高校学风建设及电子信息学科教学改革等方面起到了引导和推进作用。

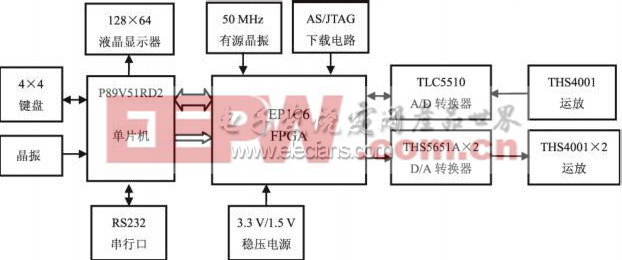

大学生电子竞赛题目以模拟电子、数字电子、可编程逻辑器件及单片机技术为核心, 涉及电子仪器仪表、通信、高频无线电、自动控制等多学科内容。2007 年电子设计竞赛组委会专家指出: 电子设计竞赛的发展趋势将以模电、数电、FP2GA 为重点。因此, 对于参赛队员来说要获得较好的成绩, 选择合适的题目并进行培训至关重要。笔者针对以FPGA 为核心的竞赛题目特点及竞赛元器件要求, 设计制作了竞赛电路板, 组成框图如图1 所示。

图1 电子竞赛电路板组成框图

本设计主要包括3 个部分: 单片机扩展电路、FPGA 核心电路、高速A/ D 和D/ A 转换电路。其中单片机扩展电路主要包括振荡电路、液晶显示模块接口、按键、复位电路等,这部分既可以进行基本的单片机实验, 还可以为FPGA 核心电路提供控制信号及利用FPGA 的资源等; FPGA 核心电路部分主要由电源、J TAG 下载、AS 下载、输入输出电路等组成; 高速A/ D 和D/ A 转换电路具有一路模拟信号输入、两路模拟信号输出。设计将3 部分有机地结合在一起, 组成了一个实验系统, 它既能够完成等精度频率计、DDS 信号发生器、数字示波器等竞赛题目的设计, 又可以用于赛前培训。

1 电路设计

1. 1 FPGA 核心电路板。

1. 1. 1 FPGA 芯片选择

FPGA是英文Field Programmable Gate Array 的缩写,即现场可编程门阵列,它是在PAL, GAL, EPLD 等可编程器件的基础上进一步发展的产物。它是作为专用集成电路( ASIC)领域中的一种半定制电路而出现的, 既解决了定制电路的不足, 又克服了原有可编程器件门电路数量有限的缺点。

经过分析近几届电子设计竞赛中的题目, 发现设计题目对FPGA 的功能要求不是太高, 一般常用的FPGA 都能满足设计要求。通过比较, 知道Alter a 公司的Cyclone 系列FPGA具有低成本的特点, 而且平衡了逻辑、存储器、锁相环和高级I/ O 接口。所以Cyclone 系列FPGA 是设计的最佳选择。

Altera 公司Cyclone 系列中的EP1C3, EP1C6, EP1C12完全能够满足设计题目要求, 所以可以从这几种芯片里选择FPGA.综合比较选择了EP1C6 系列的芯片, 这个系列中的EP1C6T 144C8 完全能够满足电子大赛的要求。而且EP1C6T 144C8 也支持SOPC ( System On Pr ogrammingChip) , 可以实现嵌入式的软CPU( 如NIOSII 等) , 为嵌入式电子设计提供了又一种选择。所以在此选择EP1C6T144C8作为此设计的FPGA 芯片。EP1C6T144C8 内部具有5 980个逻辑单元( LE) 、20 个M4K RAM 块、92 160 位嵌入式RAM、2 个锁相环、96 个I/ O 口, 支持AS、JTAG 下载, 采用TQFP144 封装形式。

1. 1. 2 FPGA 电路板设计

EP1C6T144C8 是144 脚的FPGA 芯片, 引脚分类及功能如下:

( 1) 电源引脚。使用3. 3 V 电压作为供电电源, 可以为满足各种数据传输标准的输出缓存器的提供电源, 也可以为满足LVT TL, LVCMOS, 各种PCI 接口标准的输入缓存器提供电源。

( 2) 内部逻辑门的电源引脚。使用11 5 V 电压作为供电电源, 可以为满足LVDS, SSTL2, SST L3 接口标准的输入缓存器提供电源。

( 3) 锁相环的电源引脚。锁相环的电源无论是否使用,必须将此引脚连接到11 5 V 供电电源。

( 4) 配置引脚。包括为JTAG 边界扫描测试配置接口和AS 主动串行配置接口。

( 5) 用户I/ O 口引脚。FPGA 芯片的用户I/ O 引脚为96个, 通过双排插座引出。这些接口分为3 类: 与单片机的接口、扩展接口、与A/ D 转换器及D/ A 转换器的接口。

( 6) 时钟引脚。采用50 MH z 有源晶振, 输出时钟信号经低阻值电阻缓冲后接CLK0, 即FPGA 的管脚16.

1. 2 单片机扩展接口电路设计

评论