FPGA并行数字序列传输与接口技术的研究和应用

1 引言

本文引用地址:https://www.eepw.com.cn/article/150112.htmFPGA 技术在国内外经过历时十余载的以硬件、系统及应用设计为主要内容的迅速发展 之后,其现代信息处理与控制技术的发展已开始崛起。显然,一系列以乘法和加法为主的现 代信息处理算法能够发挥FPGA 全并行算法的优势,然而,算法中反复遇到的数字信息在节 点与模块之间的序贯传递和交接,则给多路并行处理过程带来了时差和异步的问题。例如, 系统辨识[1]的最小二乘参数估计算法中,信息压缩矩阵与模型参数估计向量在并行地进行着 递推计算,而无数次循环的中间结果则需要进行首尾交接;人工神经网络[2]的训练与执行中 同一层的所有节点的各路输入在进行着并行的加权求和与活化函数的代入计算,但层与层之 间则需要进行节点间的数据交错传递;同样,Kalman 滤波[3]算法中的观测向量、状态向量、 控制向量与噪声向量都在相邻的两个时刻之间进行着数据传递。由于在同一层次上被并行地 执行的各路的行进速度并不相同,交接的过程就需要互相等待,整个过程就需要统一控制, 否则将会出现数据丢失或传输阻塞。

本文将从硬件结构与功能的Verilog 语言数据流描述的角度,逐层讨论问题的解决办法 。

2.1 模块内的数据传输

在一个模块内,变量之间的数据传输接口的性质可分别用 reg(寄存功能,有延时性) 和wire(连线功能,无延时性)来定义。Reg 型常表示“always”( 触发器)模块的指定信 号,前者由后者通过使用行为描述语句来表达逻辑关系。

而wire 型常表示“assign”关键字的制定组合逻辑信号。当输入输出信号类型默认时自 动定义为wire 型。wire 型信号可以用作任何方程式的输入,并且wire 型变量通常是用来表 示单个门驱动或连续赋值语句驱动的网络型数据。

2.2 模块间的数据传输

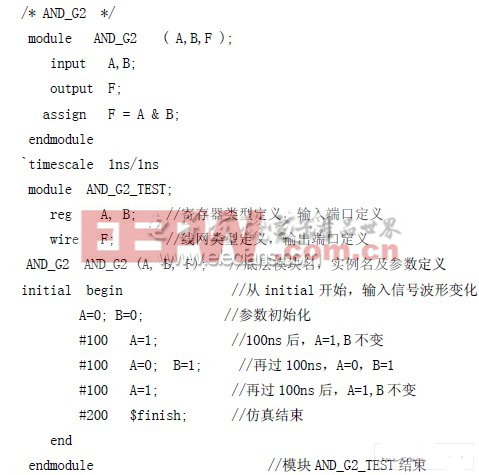

模块间的数据传输接口例如延时输出寄存器,它是一个使用了可控延时寄存器功能的AND 逻辑模块(记作AND_G2)的数据流描述如下:

该程序中AND_G2_teST 为顶层模块,AND_G2 作为一个单独的模块被顶层模块所调 用。通过综合控制,A、B 的输入信号达到同步。

3 FPGA-信息处理实例—简单人工神经网络设计

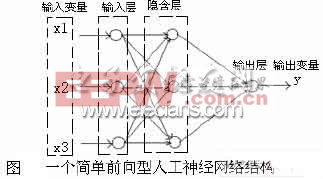

一个包括三个输入、单个输出、一个三节点隐含层的前向型人工神经网络结构如图1 所示。下面从多个角度讨论数据的处理与传输。

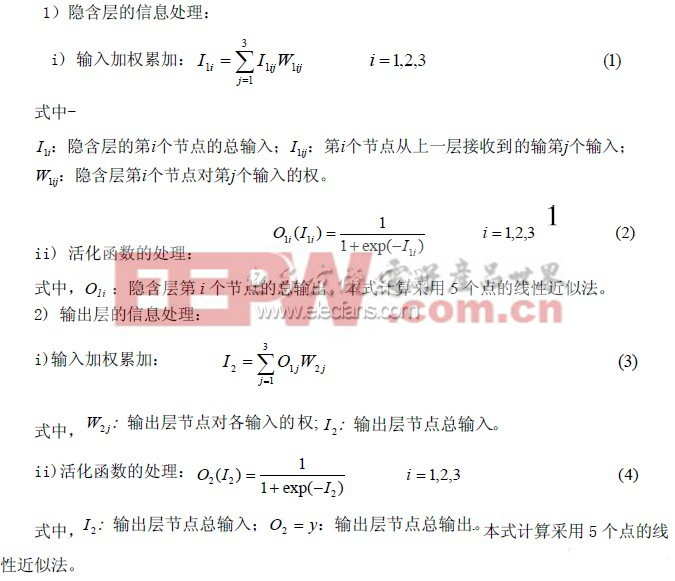

3.1 信息处理数学过程为:

评论