Vivado Design Suite 用户指南:动态功能交换

FPGA 技术支持灵活开展现场编程和再编程,无需通过设计修改来重建互连结构。Dynamic Function eXchange (动态功能交换,DFX)推动这一灵活性进一步发展,允许通过加载动态配置文件(通常是部分 BIT 文件)来修改工作中的 FPGA 设计。在使用完整 BIT 文件配置 FPGA 后,可下载部分 BIT 文件以修改 FPGA 中的可重配置区域,在未经重配置的器件各部分中运行的应用的完整性则不会受到任何影响。

DFX 是由多个部分组成的综合性解决方案。这些要素包括:AMD 芯片能进行动态重配置,Vivado® 软件流程支持编译设计(从 RTL 到比特流),以及各种补充性功能特性(如 IP)。在此版本中,您将看到 DFX 与部分重配置( PR )术语混用,其中 DFX 表示整体解决方案,PR 则表示该解决方案的技术组成部分。

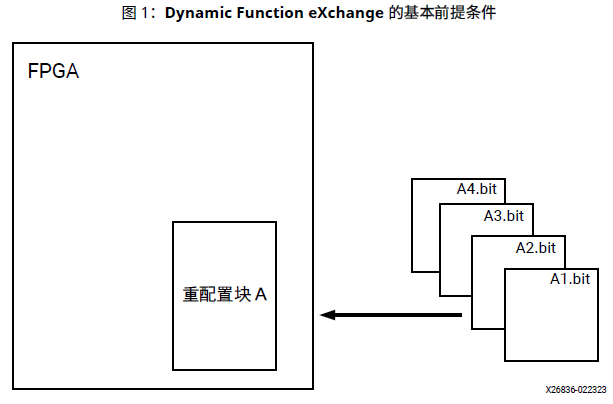

下图显示了 Dynamic Function eXchange 背后的前提条件。

如图所示,通过下载下列任一部分 BIT 文件即可修改重配置块 A 中实现的函数:A1.bit、A2.bit、A3.bit 或A4.bit。FPGA 设计中的逻辑分为 2 种不同类型:可重配置逻辑和静态逻辑。FPGA 块的灰色区域表示静态逻辑,块中标记为重配置块 A 的部分则表示可重配置逻辑。静态逻辑保持正常工作,不受加载部分 BIT 文件的影响。可重配置逻辑则替换为部分 BIT 文件的内容。

在单一 FPGA 上对多路复用硬件进行动态定时的能力是很有用的,原因有很多。其中包括:

▅ 减小实现给定函数所需 FPGA 的大小,从而降低成本和功耗

▅ 支持灵活选择可用于某一应用的算法或协议

▅ 启用设计安全性方面的新技术

▅ 改善 FPGA 容错能力

▅ 加速可配置计算

▅ 向已部署的系统交付更新(修订和新增功能特性)

除了减小大小、降低权重、功耗和成本外,Dynamic Function eXchange 还能支持无法以其它方式实现的多种新型 FPGA 设计。

*博客内容为网友个人发布,仅代表博主个人观点,如有侵权请联系工作人员删除。

相关推荐

LabVIEW FPGA 模块简介

基于FPGA的可编程数字滤波器系统

help, 44b0+fpga拖死cpu

基于FPGA的锁相环位同步提取电路

视频协议板-FPGA配置基于LatticeECP3的设计

3-DES算法的FPGA高速实现(Xilinx)

FPGA如何同DDR3存储器进行接口?

help, 44b0+fpga拖死cpu

Altera: 采用全系列40-nm收发器FPGA和ASIC实现创新

ALTERA的PCI_IP Core问答集

特朗普政府或将实施全球AI芯片出口管制,英伟达与AMD恐受波及

Altera公司cyclone系列FPGA-1C6电路图

美国政府拟对英伟达、AMD人工智能硬件实施全面出口管制

LatticeECP3设计的视频协议板电路图-FPGA配置

DC到3.2GHz采样率!PXI平台+开放FPGA赋能,我们打造了一款“软件定义”的锁相放大器

CPU借AI热潮重获青睐,再度 “变酷”

用C/C++语言开发大规模FPGA [转载于www.fpga.com.cn]

AMD 扩展锐龙 AI 嵌入式处理器产品组合

人工智能开始简化可编程逻辑的设计

LabVIEW 8.20技术资料大全简介

FPGA在边缘人工智能中日益扩大的作用

基于SD7502构成的FPGA-ASK电路图

help, 44b0+fpga拖死cpu

s3c2410+fpga 做视频无线传输

利用锚定可信平台模块(TPM)的FPGA构建人形机器人安全

Altera的FPGA下载常见问题经验小结

AMD 扩展锐龙 AI 嵌入式处理器产品组合,为工业与 AI 边缘解决方案提供可扩展的高效 AI 计算能力

高速ADC与内置嵌入式串行收发器的FPGA接口

贸泽电子开售:面向工业、AI、医疗、数据中心等领域的Altera Agilex 5 FPGA与SoC

实时的噪声源定位系统