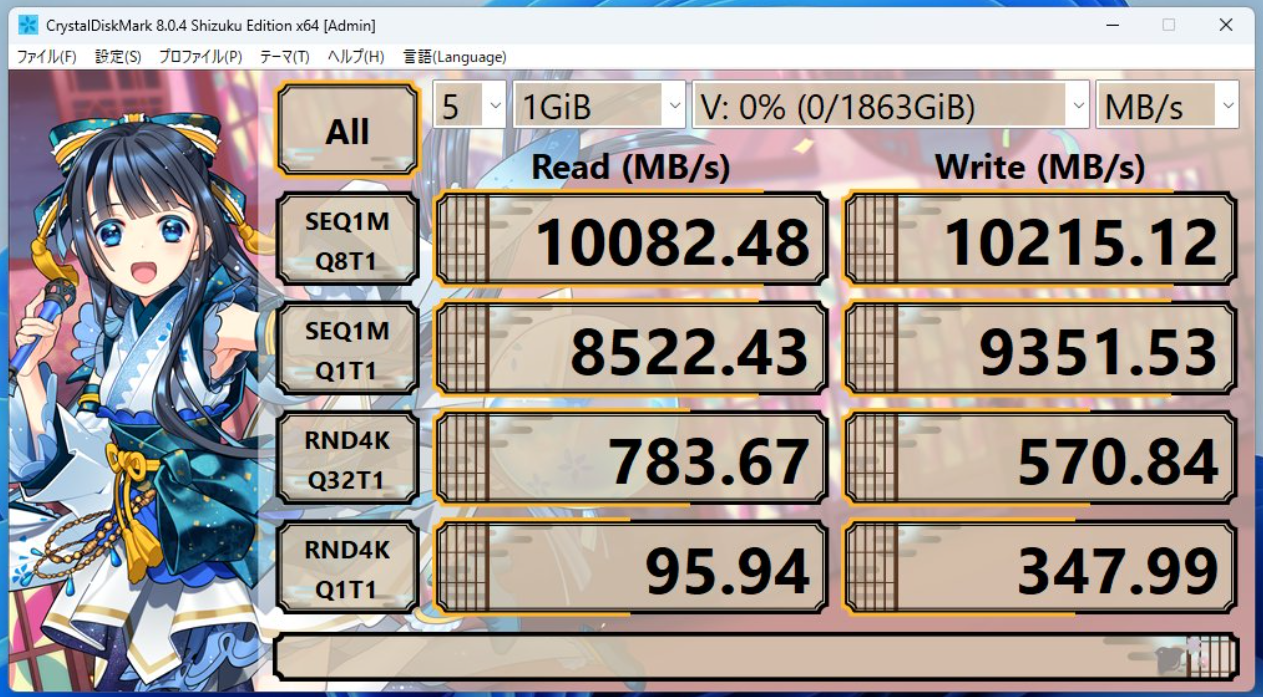

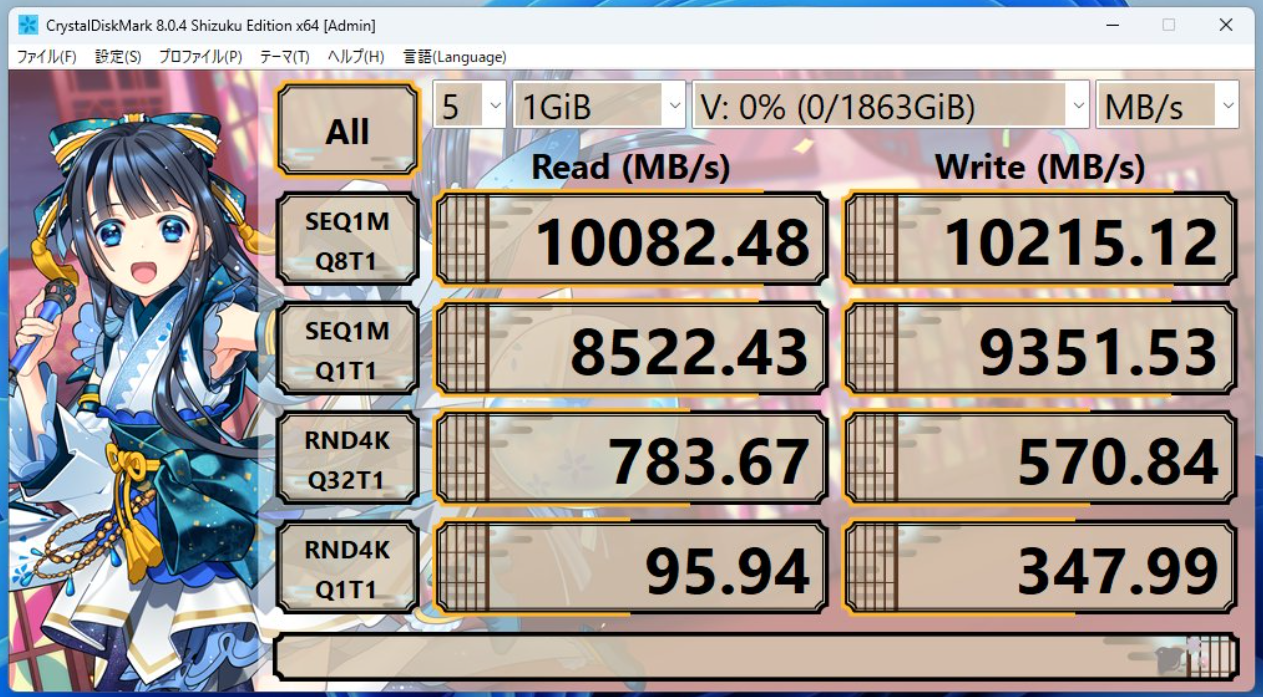

- IT之家 2 月 5 日消息,日本厂商 CFD Gaming 此前率先开卖了 PCIe Gen 5.0 SSD,2TB 售价 49980 日元(当前约 2604 元人民币),现在已经有博主拿到了这款产品。根据推特博主 @momomo_us 晒出的图片,他已经拿到了这款 SSD,使用 CrystalDiskMark 进行的基准测试确认,该 SSD 可以轻松超过 10 GB / s 的顺序读写速度。不过,较小的容量写入速度会略微降低(~9.5 GB / s)。此外,SSD 的风扇

- 关键字:

PCIe 5.0 SSD

- 近日,三星宣布高性能PCIe 4.0 NVMe SSD(固态硬盘)——PM9C1a的生产工作准备就绪。PM9C1a是基于三星5纳米(nm)高端工艺和第七代V-NAND技术的全新存储器产品,将为 PC 和笔记本电脑提供更高的计算和游戏性能。三星存储事业部执行副总裁Yong Ho Song表示,三星将持续推进PC SSD领域的创新,致力于打造多样化的存储产品,以满足不断变化的市场需求。三星的PM9C1a SSD采用PCIe 4.0接口,与其前一代存储产品PM9B1相比,PM9C1a

SSD拥有快1.6倍的

- 关键字:

三星 PM9C1a PCIe 4.0 SSD

- 倍捷连接器(PEI-Genesis)总裁兼首席执行官Steven Fisher正式宣布收购有40年历史,总部位于加州的连接、被动、和机电元器件(IP&E)供应商Testco Inc.,。Steven Fisher表示:“此次收购将为客户提供更广泛的IP&E产品方案。我们是行业值得信赖的互连专家,本次收购有助于提升我们解决互连问题的能力,更丰富的产品和服务,会进一步加强我们和客户的合作。”40年以来,Testco Inc. 为全球科技公司提供连接、被动、和机电元器件(IP

- 关键字:

倍捷连接器 IP&E Testco

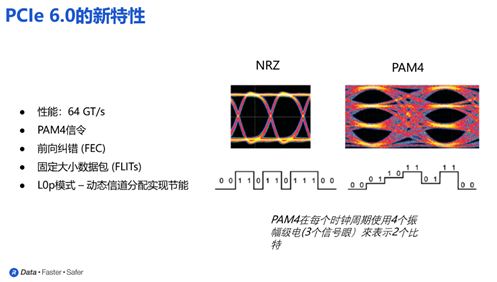

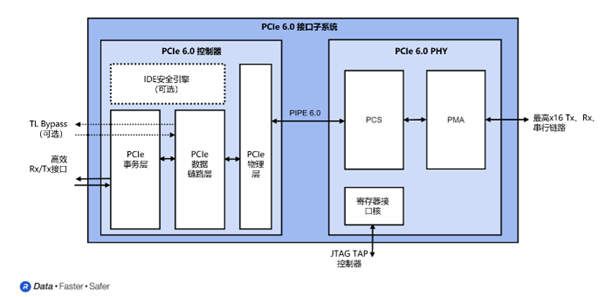

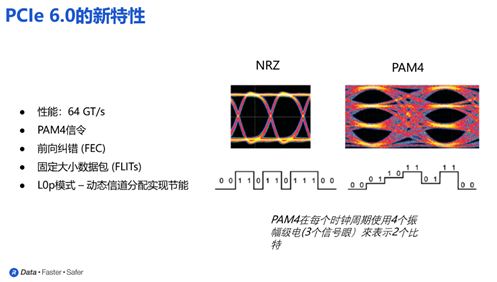

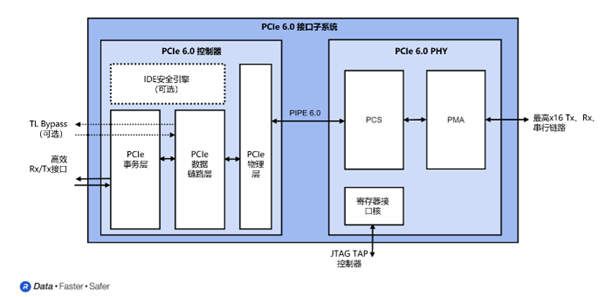

- 近日,Rambus宣布推出全球首个PCIe 6.0接口子系统,主要面向高性能数据中心、AI SoC等领域。Rambus的方案包括完整的PHY物理层、控制器IP,完整符合PCIe 6.0规范,针对异构计算架构全面优化,同时也支持最新的CXL 3.0规范,可优化内存资源。Rambus大中华区总经理苏雷介绍,Rambus作为一家业界领先的Silicon IP和芯片提供商,致力于让数据传输更快、更安全。Rambus目前的主要业务包括专利授权、IP授权,以及芯片产品。经过30多年的发展,Rambus有3000多项技

- 关键字:

PCIe 6.0 接口子系统 Rambus SoC

- 过去几年,国际形势的变化让壮大中国芯片设计产业成为中国半导体产业发展的主题,伴随着全社会对中国半导体产业的关注提升和资本的涌入,整个半导体设计产业链迎来全面的发展机遇。对中国集成电路设计产业来说,芯片设计能力的提升,不仅需要设计公司技术的提升,还需要先进的本土芯片制造能力和相关设计工具的鼎力支撑。 随着国内芯片设计企业的大量涌现,本土芯片设计带动着设计IP需求增长非常明显,这不仅给成立多年的本土IP企业发展的黄金机遇,同时也催生出大量的新兴IP初创企业,这些企业的起点高、IP运作经验丰富,共同

- 关键字:

芯来科技 RISC-V IP ICCAD

- 过去几年,国际形势的变化让壮大中国芯片设计产业成为中国半导体产业发展的主题,伴随着全社会对中国半导体产业的关注提升和资本的涌入,整个半导体设计产业链迎来全面的发展机遇。对中国集成电路设计产业来说,芯片设计能力的提升,不仅需要设计公司技术的提升,还需要先进的本土芯片制造能力和相关设计工具的鼎力支撑。 随着国内芯片设计企业的大量涌现,本土芯片设计带动着设计IP需求增长非常明显,这不仅给成立多年的本土IP企业发展的黄金机遇,同时也催生出大量的新兴IP初创企业,这些企业的起点高、IP运作经验丰富,共同为

- 关键字:

奎芯科技 Chiplet IP ICCAD

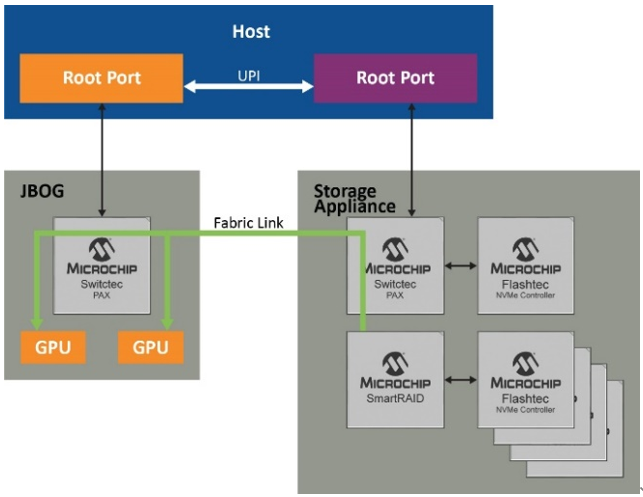

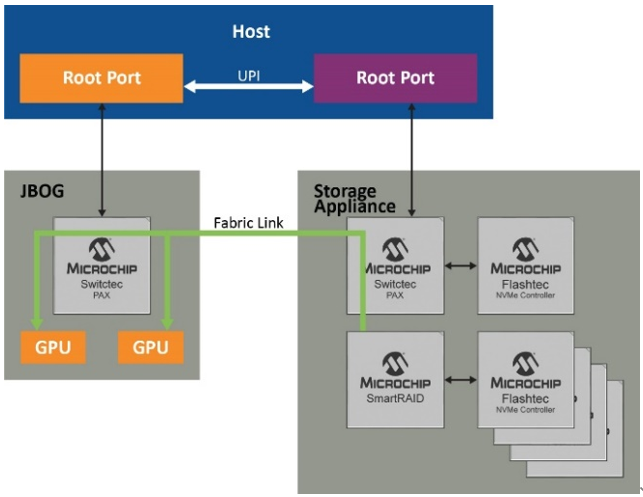

- 随着更快的图形处理单元(GPU)能够提供明显更高的计算能力,存储设备和GPU存储器之间的数据路径瓶颈已经无法实现最佳应用程序性能。NVIDIA的Magnum IO GPUDirect存储解决方案通过在存储设备和GPU存储器之间实现直接路径,可以极大地帮助解决该问题。然而,同等重要的是要使用容错系统来优化其已经非常出色的能力,从而确保在发生灾难性故障时备份关键数据。该解决方案通过PCIe®结构连接逻辑RAID卷,在PCIe 4.0规范下,这可以将数据速率提高到26 GB/s。为了解如何实现这些优势,首先需要

- 关键字:

PCIe RAID GPUDirect存储

- IT之家 12 月 27 日消息,据 SK 海力士官方消息,SK 海力士将参与明年 1 月 5 日至 8 日在美国拉斯维加斯举行的“CES 2023”,展示主力存储器产品和新的产品阵容。据介绍,此次 SK 海力士展示的核心产品是超高性能企业级 SSD 产品 PS1010 E3.S。官方称,PS1010 是由多个 SK 海力士的 176 层 4D NAND 结合而成的模组产品,支持 PCIe 第五代 (Gen 5) 标准。PS1010 与上一代相比,读写速度分别最高提升了 130% 和 49%。另

- 关键字:

PCIe 5.0 SSD PS1010

- 德国慕尼黑,2022年12月7日——处理器设计自动化和RISC-V处理器IP的领导者Codasip今日宣布成立Codasip实验室(Codasip Labs)。作为公司内部创新中心,新的Codasip实验室将支持关键应用领域中创新技术的开发和商业应用,覆盖了安全、功能安全(FuSa)和人工智能/机器学习(AI/ML)等方向。该实验室的使命在于识别和构建相关技术,以扩展定制计算的可能性,并加快具有定制化的、领域专用设计的差异化产品的开发,并缩短其上市时间。Codasip实验室将由公司创始人兼总裁马克仁(Ka

- 关键字:

Codasip Codasip 实验室 IP RISC-V

- 作为业界领先的芯片和半导体IP供应商,致力于使数据传输更快更安全,Rambus Inc.(纳斯达克股票代码:RMBS)今日宣布,推出由PHY和控制器IP组成的PCI Express®(PCIe®)6.0接口子系统。Rambus PCIe Express 6.0 PHY还支持最新版本(3.0版本)的Compute Express Link™(CXL™)规范。 PCIe 6.0接口子系统(图片来源:Rambus Inc.) Rambus接口IP总经理Scott Houghton表示:“人工

- 关键字:

Rambus 数据中心 人工智能 SoC PCIe 6.0 接口子系统

- 【2022 年 11 月 29 日美国德州普拉诺讯】Diodes 公司 (Diodes) (Nasdaq:DIOD) 将推出其最新的 PCIe® 3.0 数据包切换器 DIODES™ PI7C9X3G1224GP。此产品是一款高效能 12 端口、24 信道装置产品,可用于边缘运算、数据储存装置、通讯基础设施,并整合到主机总线配接器 (HBA)、工业控制器及网络路由器中。PI7C9X3G1224GP 的低数据包转发延迟小于 150ns (典型值)。透过每个端口分配可变通道宽度的范围,实现此装置的弹性端口组态

- 关键字:

Diodes PCIe 3.0 数据包切换器

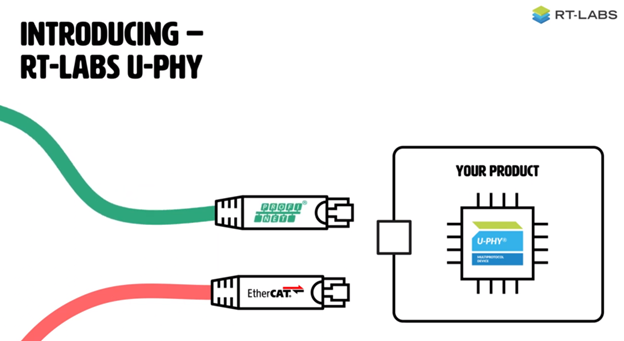

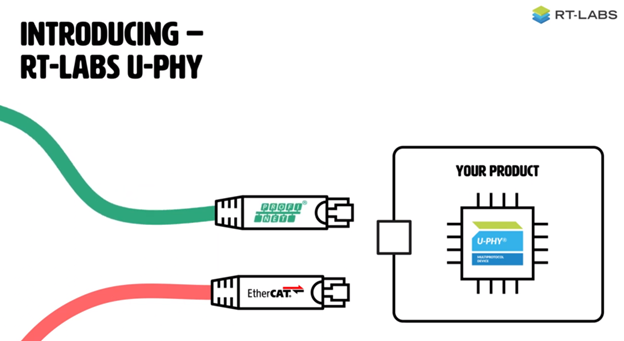

- 瑞典哥德堡,2022年11月23日 – RT-Labs今天宣布推出一种全新、基于软件的解决方案U-Phy,工业设备开发者可以借助该解决方案在开放硬件设计上实现两种最流行的工业通信协议(现场总线):Profinet和EtherCAT。通过采用U-Phy,开发者可以获得更高灵活性,无需对某些供应商过度依赖,同时减少开发时间和成本。作为预先认证的解决方案,RT-Labs不需要关于具体协议的专门知识。基于版税的专用集成电路(ASIC)或专用通信模块已成为工业设备(如传感器和致动器)通过现场总线网络与其他

- 关键字:

RT-Labs 现场总线 U-Phy

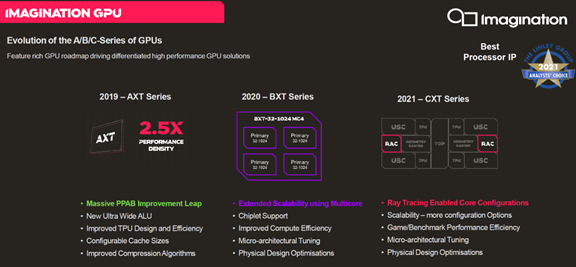

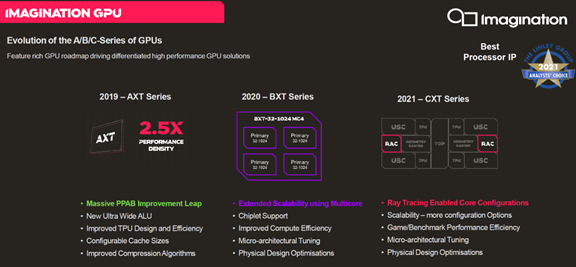

- 过去50余年,芯片制程迭代沿着摩尔定律滚滚向前,并持续增强着芯片的算力与性能。现如今,无论是在SoC上集成越来越多的功能模块,又或是利用chiplet技术在先进制程下进一步提升芯片集成度,都充分展现了芯片性能、功耗和成本的改进不能仅仅依赖于制程的升级,而需从不同的维度拓展创新来延续摩尔定律的“经济效益”。这导致芯片设计变得越来越困难,IP的作用也愈加凸显,逐渐成为企业寻求设计差异化道路上的“秘钥”。 日前,在深圳举办的第10届EEVIA年度中国硬科技媒体论坛暨产业链研创趋势展望研讨会上,Imag

- 关键字:

IP Imagination

- 在庞大的半导体细分产业链中,IP是其中最特殊的一环。正是借助众多的IP,才让半导体发展的步伐如此之快。IP是整个半导体上游产业链里面的核心,根据统计数据可以发现,每一元芯片能撑起200多元的社会经济,而每一元的IP,能支持20000元的社会经济价值,所以IP公司的存在是必要的。 随着芯片复杂度不断提升,特别是芯片进入SoC时代使得系统对各个环节技术要求越来越高,对一些中小型公司、创业公司来说,他们需要在成长过程中专注核心领域,没办法提供整个SoC完整的技术,所以它需要IP公司的支持,IP公司能协

- 关键字:

Imagination SoC IP GPU

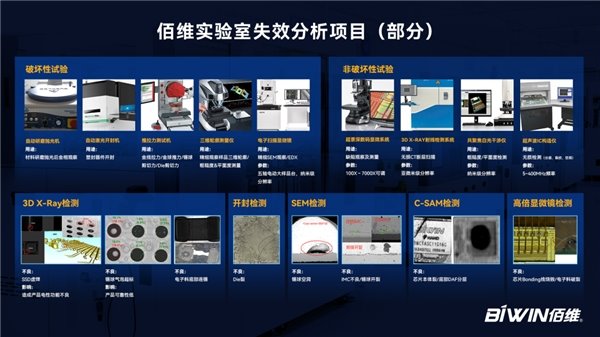

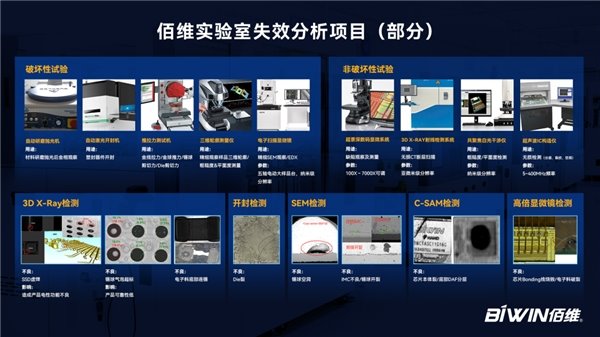

- 在半导体存储器领域,佰维存储构筑了研发封测一体化的经营模式,有力地促进了自身产品的市场竞争力。以佰维 EP400 PCIe BGA SSD 为例,公司优秀的存储介质特性研究与固件算法开发能力,大大提升了该款产品的性能和可靠性;相应地,佰维布局的先进封测能力又对该款产品的竞争力达成有哪些帮助呢,请跟随我们的分析一探究竟吧。16 层叠 Die、40μm 超薄 Die 先进封装工艺,突破存储容量限制芯片封装是集成电路产业链中的关键一环,主要用来保障芯片在实现具体功能时免受污染且易于装配,在实现电子互联与信号通讯

- 关键字:

佰维存储 佰维 EP400 PCIe SSD

pcie 4.0 phy ip介绍

您好,目前还没有人创建词条pcie 4.0 phy ip!

欢迎您创建该词条,阐述对pcie 4.0 phy ip的理解,并与今后在此搜索pcie 4.0 phy ip的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473