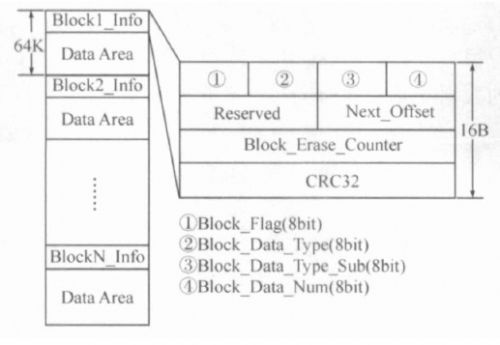

- 随着嵌入式系统产品的发展,对存储设备的要求也日益增强。文章以东芝的NAND E2PROM器件TC58DVG02A1F00为例,阐述了NAND Flash的基本结构和使用方法

- 关键字:

Flash NAND 02A 1FT

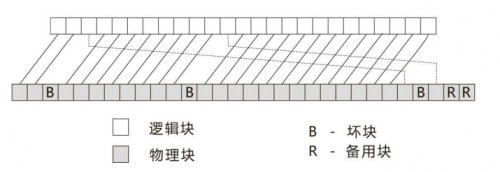

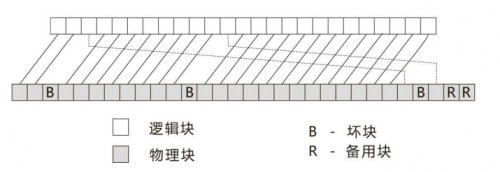

- 被广泛应用于手机、平板等数码设备中的Nand Flash由于工艺原因无法避免坏块的存在,但是我们可以凭借高科技变废为宝,将“坏块”进行有效的利用,从而满足我们的应用需求,让坏块不“坏”。

要想变废为宝,有效利用坏块。我们首先要弄明白什么是“坏块”,做到知己知彼,才能为我所用。坏块的特点是当编程或者擦除这个块时,不能将某些位拉高,从而造成编程和块擦除操作时的错误,这种错误可以通过状态寄存器的值反映出来。这些无效块无法确定编程时

- 关键字:

Nand Flash 寄存器

- 摘要在嵌入式设计中,许多应用设计都需要使用EEPROM 存储非易失性数据,由于成本原因,某些单片机在芯片内部并没有集成EEPROM。MSP430G 系列处理器是TI 推出的低成本16 位处理器,在MSP430G 系列单片机中并不具备E

- 关键字:

MSP430G 单片机 Flash

- FLASH 和EEPROM的最大区别是FLASH按扇区操作,EEPROM则按字节操作,二者寻址方法不同,存储单元的结构也不同,FLASH的电路结构较简单,同样容量占芯片面积较小,成本自然比EEPROM低,因而适合用作程序存储器,EEPROM则更多的用作非易失的数据存储器。当然用FLASH做数据存储器也行,但操作比EEPROM麻烦的多,所以更“人性化”的MCU设计会集成FLASH和EEPROM两种非易失性存储器,而廉价型设计往往只有 FLASH,早期可电擦写型MCU则都是EEPRM结构,现在已基本上停产了。

- 关键字:

单片机 flash eeprom

- 首先需要了解NAND FLASH的结构。如图:以镁光MT29F4G08BxB Nand Flash为例,这款Flash(如上图)以4个扇区(sector)组成1个页(page),64个页(page)组成1个块(block),4096个块(block)构成整个Flash存储器;由于每个扇区

- 关键字:

Flash NAND 扇区管理

- JEDEC标准(JESD216)Serial Flash Discoverable Parameter (SFDP)[1]是在串行Flash中建立一个可供查询的描述串行Flash功能的参数表。文章主要介绍了这个串行Flash功能参数表的结构、功能和作用,并给出其在系统设计中的具体应用。

- 关键字:

JEDEC Flash JESD

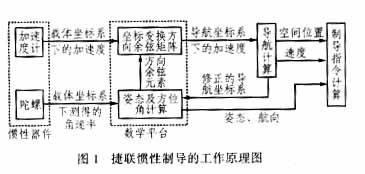

- TMS320C6455 DSP基于外部FLASH自动加载的设计,摘要 为实现数字信号处理器的加栽,介绍了TMS320C6455的各种加载模式,尤其是对外部ROM的引导方式,以及一种无需数据转换即可通过数据加载将用户程序写入Flash的方法。以TMS320C6455为例,同时结合LED灯闪烁实例验证

- 关键字:

DSP 加栽模式 二次加载 Flash

- 全球NAND Flash(储存型快闪记忆体)供给成长持续大于需求,预估NAND Flash今年底报价将较去年跌掉三成,且跌势恐将一直延续至2018年。市调机构IHS iSuppli最

- 关键字:

三星 东芝 NAND Flash

- 多款采用威盛(VIA)第二代Nano平台的All-in-One计算机、小笔记本,乃至于OLPC计划的XO小笔电1.5代,都将在今年CES展亮相。威盛第二代Nano平台,是以去(09)年

- 关键字:

威盛 Nano Atom

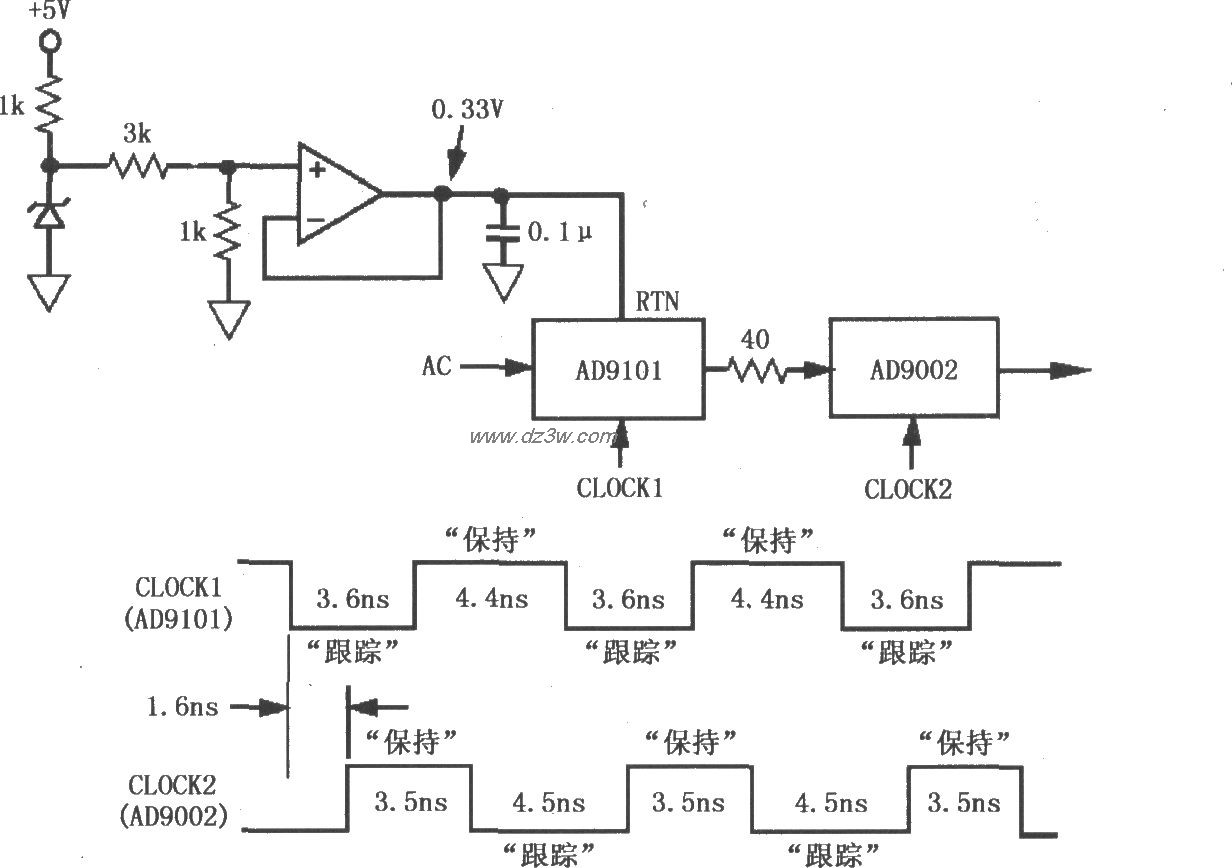

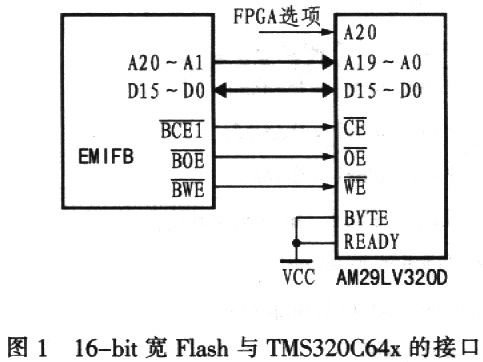

- 数字信号处理芯片(DSP) 具有高性能的CPU(时钟性能超过100MHZ)和高速先进外围设备,通过CMOS处理技术,DSP芯片的功耗越来越低。这些巨大的进步增加了DSP

- 关键字:

硬件设计 FlaSh DSP

- 使用LPC2106的Timer 1 进行的简单的中断处理。示例代码中Timer1分为FIQ和IRQ,用户可以从Flash或者SRAM中运行这些代码。示例展示了ARM构架中中断是如何操作

- 关键字:

Flash SRAM 触发中断

- 市调机构集邦科技旗下存储器储存事业处DRAMeXchange调查显示,第4季各项NAND Flash终端需求确立旺季不旺,加上厂商库存水位依旧偏高,采购意愿薄弱,

- 关键字:

NAND Flash

- 在加州硅谷圣荷塞举行的嵌入式系统大会ESC 2010上,VIA正式宣布推出Nano E系列处理器,为嵌入式市场带来原生64位软件支持、虚拟化能力和更长生命周期

- 关键字:

VIA Nano

- 如何用SmartPRO 6000纠正NAND Flash烧录过程位反转,关于使用烧录器烧录Nand Flash,一直都是很多用户头疼的难点,他们强调已经使用了正确的坏块管理方案,也制定了规范的操作流程,但是烧录的良品率还是无法提高,只能每天眼睁睁看着一盘盘“废品”被烧录器筛选出来!

- 关键字:

烧录 SmartPRO 6000 Nand Flash

nano nor flash介绍

您好,目前还没有人创建词条nano nor flash!

欢迎您创建该词条,阐述对nano nor flash的理解,并与今后在此搜索nano nor flash的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473