Analog Devices, Inc. (ADI: NASDAQ) 最近推出一款快速原型制作套件,其可简化宽动态范围 GSPA 数据转换器到 FPGA(现场可编程门阵列)的连接。 数字和模拟设计人员可以采用快速原型制作套件 AD-FMCDAQ2-EBZ ,在主要的 FPGA 平台(包括 Xilinx 的 UltraScale FPGA,以及 Zynq 用于雷达、仪器仪表、无线电和其它数据采集应用的所有可编程 SoC 器件)上快速地对高速 JEDEC JESD204B SerDes(串行器/解串器)G

关键字:

ADI FPGA SoC

十年前,诺基亚和摩托罗拉等手机巨擘基本上不会理睬台湾联发科技生产的芯片,而是雇用大量工程师对电子部件和电路系统进行评估。

快速前进到智能手机时代。

智能机市场中充斥着中国手机制商,他们推出廉价手机与苹果和三星电子争夺市场份额。台湾的联发科技是廉价智能手机兴起的推动者。奉行薄利多销策略的手机制造商对联发科技的芯片青睐有加。

联发科技最先将镜头和扬声器等硬件与低成本芯片进行功能集成。这种系统级芯片(SoC)让手机制造商不再需要自己花钱寻找和测试能够与其采购的芯片相匹配的部件。这反过来有助

关键字:

联发科 SoC 智能手机

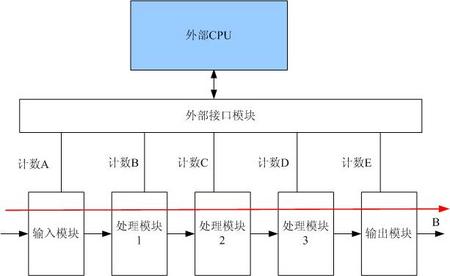

如果设计中有多个模块,每个模块内部有许多寄存器或者存储块需要配置或者提供读出那么实现方式有多种,主要如下:

实现方式一:可以在模块顶部将所有寄存器引出,提供统一的模块进行配置和读出。这种方式简单是简单,但是顶层连接工作量较大,并且如果配置个数较多,导致顶层中寄存器的数目也会较多。

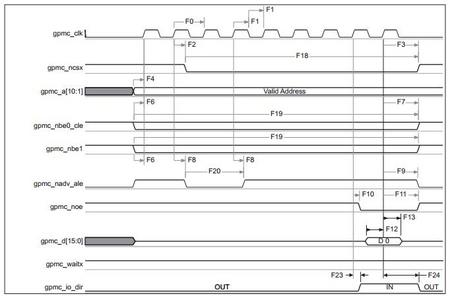

实现方式二:通过总线进行连接,为每个模块分配一个地址范围。这样寄存器等扩展就可以在模块内部进行扩展,而不用再顶层进行过多的顶层互联。如下图所示:

那如果进行总线的选择,那么有一种

关键字:

FPGA AVALON

有个笑话说,有个病人感冒了,于是去看医生,医生诊断后说,你得了感冒,但是我只会治疗肺炎,不如你回家再浇点凉水,把病恶化成肺炎,那我能治了。这个笑话展示了庸医误人。但是另一方面,从逻辑上来讲,医生则是一个把未知问题转化成已知问题的高手。

不说笑话,下面出两个题目,其分别是

问题1:运用数字电路,如何将一个时钟域的上升沿,转换成另一个时钟域的脉冲信号(单周期信号)。

问题2:运用数字电路,如何将一个时钟域的脉冲信号(单周期信号),转换成另一个时钟域的上升沿。

可能乍一看,这两个题目

关键字:

FPGA 数字电路

当下,最火的学问莫过于《大数据》,大数据的核心思想就是通过科学统计,实现对于社会、企业、个人的看似无规律可循的行为进行更深入和直观的了解。FPGA的可测性也可以对FPGA内部“小数据”的统计查询,来实现对FPGA内部BUG的探查。

可测性设计对于FPGA设计来说,并不是什么高神莫测的学问。FPGA的可测性设计的目的在设计一开始,就考虑后续问题调试,问题定位等问题。要了解FPGA可测性设计,只不过要回答几个问题,那就是:

(1) 设计完成如何进行测试?

(2)

关键字:

FPGA JTAG

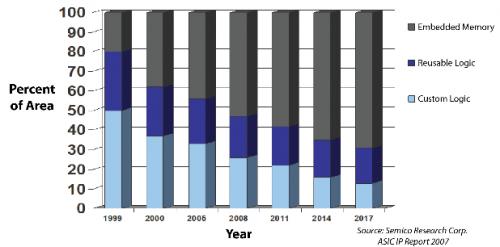

在传统的大规模ASIC和SoC设计中,芯片的物理空间大致可分为用于新的定制逻辑、用于可复用逻辑(第三方IP或传统的内部IP)和用于嵌入式存储三部分。

当各厂商为芯片产品的市场差异化(用于802.11n的无线DSP+RF、蓝牙和其他新兴无线标准)而继续开发各自独有的自定义模块,第三方IP(USB核、以太网核以及CPU/微控制器核)占用的芯片空间几乎一成未变时,嵌入式存储器所占比例却显著上升(参见图1)。

图1:当前的ASIC和SoC设计中,嵌入式存储器在总可用芯片

关键字:

ASIC SoC 存储器

“更简于新 更快于行”的英特尔架构安卓创新策略媒体沟通会上,英特尔公司中国区中国技术创新生态圈销售部及产品市场部总监杨彬先生、英特尔软件与服务事业部中国区总经理何京翔先生,分享了英特尔在安卓生态系统中的创新策略,包括从系统平台、开发工具、应用程序再到用户体验的全方位支持。同时,比亚迪、播思、乐蛙等合作伙伴还共同探讨了基于英特尔架构安卓平台的差异化优势、未来发展格局,以及将会面临的机遇与挑战。

英特尔架构+安卓平台:稳步发展 追求卓越

近年来,基于安卓平台的设备及其生

关键字:

英特尔 安卓 SOC

横跨多重电子应用领域、全球领先的半导体供应商意法半导体(STMicroelectronics,简称ST)宣布STCOMET智能电表SoC平台通过新的重要技术协议认证[i](protocol certifications),将进一步强化开发生态系统,建立一个标准统一且具有前瞻性的产品平台,符合全球主要供电企业所用的电力线通信(PLC, power-line communication)标准。

通过G3-PLC Alliance[ii]组织在2014年9月公布的G3-PLCTM认证测试项目需要的两颗

关键字:

意法半导体 智能电表 SoC

Altera公司今天宣布,使用MathWorks的业界标准工作流程,为其基于ARM的SoC提供新支持。MathWorks 2014b版包括了适用于Altera SoC的自动、高度集成、基于模型设计的设计工作流程。设计人员使用这一流程可以在高级编程环境中加速Altera SoC中的算法设计,节省了数星期的开发时间。

MathWorks信号处理应用资深策略师Ken Karnofsky说:“今天的发布极大的拓展了我们与Altera的合作,使我们的客户能够迅速方便的采用Altera SoC带

关键字:

Altera MathWorks SoC

对一些刚入行的工程师来说或是电子电机的学生们来说,

类比元件的独立与整合,可能会让人傻傻的分不清,

究竟何种情况下要选择独立型元件或是高度整合的SoC?

用最安全的说法,就是端看系统应用为何。

我们都知道,半导体制程的不断演进让MCU(微控制器)或是MPU(微处理器)的性能表现不断提升,与此同时也会整合更多类比或混合讯号,甚至是离散元件,但我们也知道,市场还是有许多独立型的类比与混合讯号元件,像是ADC(类比数立讯号转换器)、DAC(数位类比讯号转换器)或是放大器元件等,都相当

关键字:

ADI 模拟元件 SoC

下一阶段的智慧生活,将会是什么样貌?ARM正不断引爆智慧生活的新革命,并擘划“隐形的智慧”未来蓝图。除此之外,ARM也持续与合作夥伴在行动装置、物联网(IoT)与伺服器等领域开花结果,显示ARM高度整合、系统化并可扩充的解决方案正一步步实现不易察觉、却无所不在的智慧生活。

Antonio说,ARM正不断引爆智慧生活的新革命,并擘划“隐形的智慧”未来蓝图。

ARM执行副总裁兼全球业务开发总裁Antonio J. Vi

关键字:

ARM 物联网 SoC

作为FPGA工程师来说,碰到新的问题是设计中最常见的事情了,技术发展趋势日新月异,所以经常会有新的概念,新的需求,新的设计等待去实现。不是每个通过BAIDU或者GOOGLE都有答案。

因此,新的设计经常会有,那如何实现?

假设,FPGA需要设计一个接口模块,那我们就需要了解一下几个问题:

(1) 同步接口还是异步接口模块;

(2) 有哪些信号,功能是什么?

(3) 信号之间时序关系是什么?

(4) 传递的效率能够达到多少;

(5) 等等!

谁会给予这些答

关键字:

FPGA 测试 接口

写在coding之前的那些铁律

(1)注释: 好的代码首先必须要有注释,注释至少包括文件注释,端口注释,功能语句注释。

文件注释:文件注释就是一个说明文:这通常在文件的头部注释,用于描述代码为那个工程中,由谁写的,日期是多少,功能描述,有哪些子功能,及版本修改的标示。这样不论是谁,一目了然。即使不写文档,也能知道大概。

接口描述:module的接口信号中,接口注释描述模块外部接口,例如AHB接口,和SRAM接口等等。这样读代码的人即可能够判断即模块将AHB接口信号线转换成SRAM接口

关键字:

FPGA coding 时序

横跨多重电子应用领域、全球领先的半导体供应商、市场领先的高清 (HD) 和超高清 (UHD) 机顶盒系统芯片 (SoC) 厂商意法半导体(STMicroelectronics,简称ST),推出全球首款内置 Android 5.0 Lollipop 的 Google Android TV 机顶盒 (STB, Set-Top Box) 平台。

有了这个新平台,用户能够使用 Android TV 以及 Android 操作系统的全部生态系统,包括当前流行的 Android 游戏、应用程序和支持服务,这

关键字:

意法半导体 SoC Android TV

1 项目背景

1.1 研究背景

LCD显示屏的应用越来越广,数量越来越多。LCD显示屏应用广泛,无处不在。小到家庭各种电器设备,大到军事设备。更常见是用于各种公共场合如体育馆、广场等商业用途。给我们传递一种更为直观、生动的信息。从此我们的生活发生了巨大改变。巨大的应用巨大的市场带来了巨大的商机。传统的显示器大多采用控制系统与显示界面集成在一起的方案,不便于实时管理与有效维护,不便于及时更新;也不便于人亲临恶劣的工作环境下进行人为操控。LED显示屏用户迫切需要实现对LED显示屏的远程控制。

关键字:

FPGA LCD Microblaze

fpga soc介绍

您好,目前还没有人创建词条fpga soc!

欢迎您创建该词条,阐述对fpga soc的理解,并与今后在此搜索fpga soc的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473