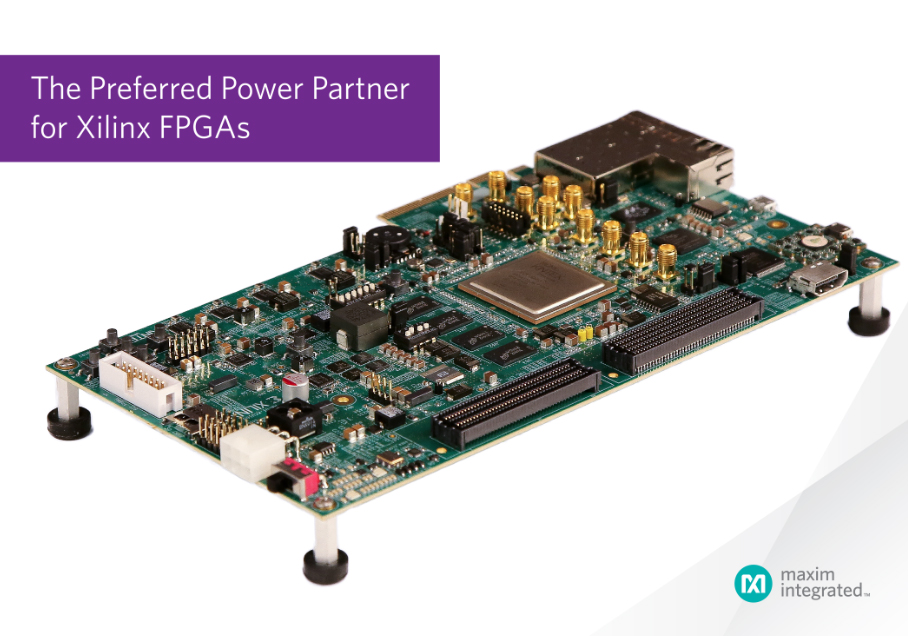

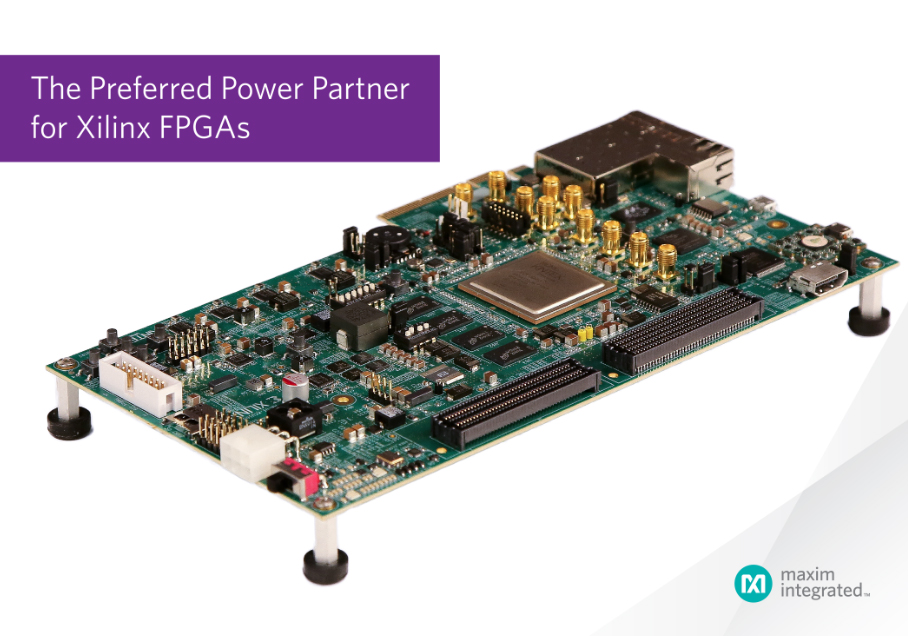

- Maxim Integrated Products, Inc. 宣布成为Xilinx UltraScale FPGA电源方案的主要供应商,Maxim为三款Xilinx FPGA参考设计提供电源管理方案。X-Fest 2014展会期间,系统设计人员可通过Xilinx Kintex UltraScale FPGA KCU105评估板对Maxim方案进行评估。

此次合作中,Maxim采用了十分灵活的InTune™数字电源产品,并首次将高密度、高效率的Volterra技术应用到FPGA开发板

- 关键字:

Maxim Integrated Xilinx FPGA

- Maxim Integrated Products, Inc. 推出高速、18位数据采集系统(DAS)参考设计MAXREFDES74#,帮助FPGA工程师加快基于FPGA控制系统的评估和验证,以及产品的上市进程。

如何实现高精度、高速数字控制环路是摆在设计人员面前的一个难题。现在,MAXREFDES74# DAS能够为要求高精度、高速数据转换的FPGA数字处理系统提供18位数据采集模拟输入和输出前端。MAXREFDES74#可直接插入标准FPGA I/O扩展口(FMC),参考设计包含完备的硬件、

- 关键字:

Maxim Integrated FPGA 数据采集系统

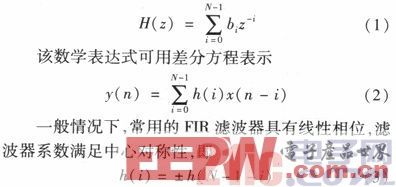

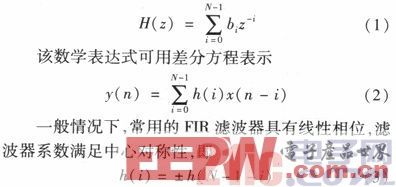

- 摘要 采用改进并行分布式算法设计了一种16抽头FIR数字低通滤波器,首先用Matlab工具箱中的FDATool设计滤波器系数,然后使用硬件描述语言Verilog HDL和原理图,实现了子模块和系统模块设计,在Matlab与QuartusII中对系统模块进行联合仿真。仿真结果表明,设计系统性能稳定,滤波效果良好,且实用性较强。

数字滤波器分为有限冲激响应(FIR)和无限冲激响应(IIR)两种。其中,FIR数字滤波器在实现任意幅频特性的同时能够保证严格的线性相位特性。由于其单位冲激响应是有限的,没有

- 关键字:

FPGA 低通滤波器 Matlab

- 下一篇:RIGOL普源精电 MSO1104Z 示波器拆解之主控芯片(FPGA)及外围芯片

四、RIGOL普源精电 MSO1104Z 示波器拆解之主控芯片(ARM)及外围芯片展示

看完了主控芯片(FPGA)以及外围的一些芯片,我们再看看另一颗主控芯片。我们可以看到这是一颗Freescale (飞思卡尔)公司的iMAX283芯片,笔者百度了有关这个芯片的介绍,有兴趣的可以看看,i.MX283 是一款低功率、高性能的多媒体应用处理器,专为通用嵌入式工业控制和消费电子市场而优化。i.MX283内核

- 关键字:

FPGA Freescale iMAX283

- 上一篇: RIGOL普源精电 MSO1104Z 示波器拆解之拆解屏蔽罩

三、RIGOL普源精电 MSO1104Z 示波器拆解之主控芯片(FPGA)及外围芯片

先来个主控板的全身照吧

主板部分我们先从主控芯片看起吧,大家猜猜看,那个是最主要的芯片,我猜一定是那个带着散热片的芯片吧。来张特写看看吧。

我们可以看到许多信号都是从这个芯片出来的,看来是主控芯片无疑了,这个主控芯片上面加了个散热片,散热片和芯片之间用导热硅胶固定着,

- 关键字:

FPGA 散热片 ADI

- 前段时间入手了普源精电的一款型号为MSO1104Z 示波器,用了一段时间,总体来说这款示波器,性能各方面都很不错,对得起这个价格,通过购买和使用这款示波器,让我对国产示波器有了新的认识,对于这款示波器的性能还挺满意,但不知道示波器内部硬件设计如何,正好周末闲来无事,手痒难耐,决定拆来看看,一来是满足自己的好奇心,因为笔者是从事FPGA开发的,也看过一些示波器的拆机图,里面有用到FPGA芯片,所以对于这款示波器是否也用到FPGA芯片以及用什么型号的FPGA芯片非常感兴趣。二来是通过拆机能为想购买此款示波

- 关键字:

FPGA 工具

- 莱迪思(Lattice)半导体公司总裁兼CEO Darin Billerbeck近日访华,带来了最新推出iCE40 Ultra产品系列,并谈了莱迪思FPGA的独特定位。

iCE40 Ultra™独家集成了红外遥控、条形码、触控、用户识别、计步器等新兴功能以及可供定制的极大灵活性,可加速移动设备的“杀手级”功能定制。相比竞争对手的方案,iCE40 Ultra FPGA在提供5倍更多功能的同时减小了30%的尺寸。并且相比以前的器件,功耗降低高达75%。

- 关键字:

莱迪思 FPGA iCE40 201409

- 8月中旬,由赛灵思公司(Xilinx)主导的“OpenHW2014开源硬件与嵌入式计算大赛”在古城西安完美落幕。决赛入围的19支团队进行了激烈的角逐,最终来自重庆大学的“随身拍智能旋翼飞行器”项目队伍成功夺冠。在之前的预赛中,来自天津大学、中科院、华中科技大学的团队分别荣获HLS挑战赛专项一等奖。

赛灵思公司全球大学计划总监Patrick Lysaght表示:“我们非常高兴地看到越来越多的高校和知名企业加入到赛灵思率先发起的开源硬件事业

- 关键字:

赛灵思 嵌入式 FPGA 201409

- Altera公司今天宣布,获得富士施乐有限公司2014年度优秀合作伙伴奖。富士施乐公司总部位于日本,在亚太地区开发、生产并销售静电复印(或者电子照相复印)以及文档相关产品和服务。这是Altera连续第二年获得富士施乐公司的优秀合作伙伴奖,Altera FPGA和SoC可编程逻辑器件和技术以其优异的技术、极高的性价比和出众的交付能力而再次获得这一最高荣誉。

富士施乐有限公司副总裁兼采购部执行总经理Tomoyuki Matsuura评论说:“多年以来,Altera一直为我们的业务提供可靠

- 关键字:

Altera FPGA SoC

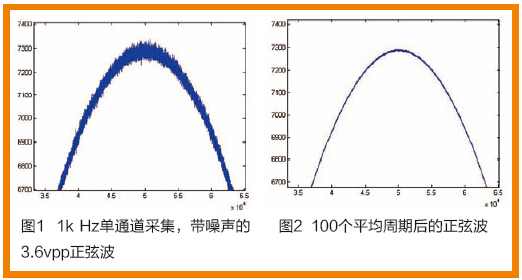

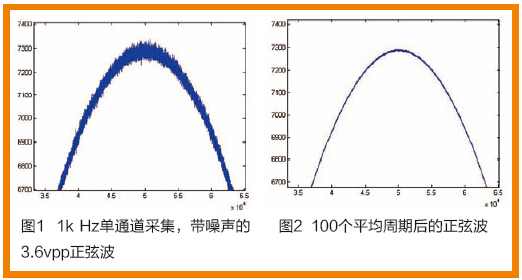

- 许多高速数据采集应用,如激光雷达或光纤测试等,都需要从嘈杂的环境中采集小的重复信号,因此对于数据采集系统的设计来说,最大的挑战就是如何最大限度地减少噪声的影响。利用信号平均技术,可以让您的测量测试系统获取更加可靠的、更加有效的测试数据。

通常情况下,在模拟信号的测试中,所采集到的数据往往夹杂着一些不需要的、随机的内容,这些数据是由周围的干扰或者测试误差所引起的,我们称之为随机噪声,这种噪声可能会影响我们的目标信号,也就是我们需要采集的数据。而采用信号平均技术,则可以减少随机噪声的影响,提升信噪比

- 关键字:

凌华 FPGA DSP PCIe-9852 201409

- 0 引 言

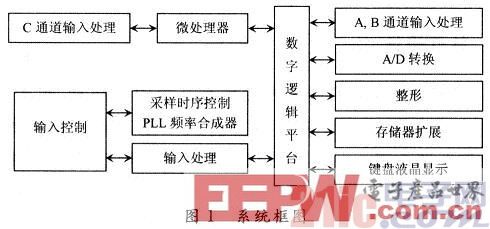

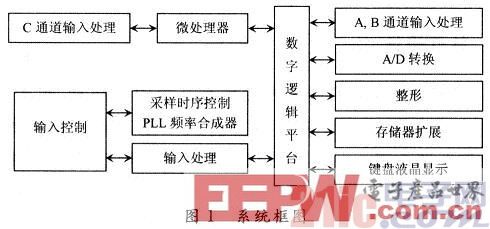

传统的数据采集系统一般采用单片机,系统大多通过PCI总线完成数据的传输。其缺点是数学运算能力差;受限于计算机插槽数量和中断资源;不便于连接与安装;易受机箱内电磁环境的影响。这些问题遏制了基于PCI总线的数据采集系统的进一步开发和应用。因此,需要一种更为简便通用的方式完成采集系统和计算机数据的交互。

数据采集系统性能的好坏,主要取决于它的精度和速度。在保证精度的条件下应尽可能地提高采样速度,以满足实时采集、实时处理和实时控制的要求。实践表明,采用ARM 32位嵌入式微处理器作为控

- 关键字:

FPGA PCI总线 ARM

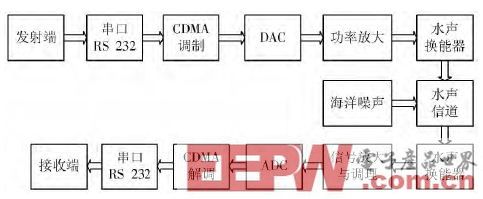

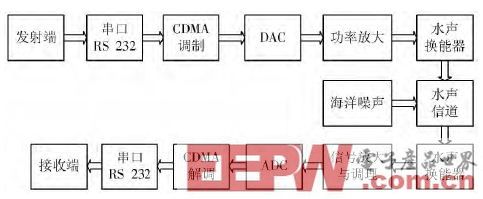

- 任何信息需要借助声、光、电信 号进行传递,由于光信号和电信号在海水中的衰减比较严重,而声波是人类迄今为止已知的惟一能在水中远距离传播的能量形势,因此,近些年海洋中的水声通信系统的研究以及开发成了热点。水声通信是指利用水声信道进行通信双方数据传输的通信系统,水声通信系统构成与传统的无线电通信系统构成具有极大的相似性,但是水声通信系统是将电信号转换成声信号,携载信息的声信号在水中进行传播完成系统的数据传输。

1 水声通信系统的总体结构

基于CDMA的水声通信调制/解调系统的设计框图如图1所示,

- 关键字:

FPGA CDMA ADS7800

- 致力于提供低功耗、安全、可靠与高性能半导体技术方案的领先供应商美高森美公司(Microsemi Corporation) 和技术研发服务领先企业eInfochips宣布共同合作为航空航天工业提供DO-254兼容设计服务。建设关键性航空电子系统的企业现在能够利用美高森美获奖的SmartFusion2®和IGLOO2®等基于FPGA产品的配置翻转免疫能力(immunity to configuration upsets),并且能够依赖eInfochips部署的先进设计实践来提升设计效率、可

- 关键字:

美高森美 eInfochips FPGA

- 看似简单的几个问题,Andrew却回答的井井有条,小编已经没有办法有什么其他词语去形容了。本文Andrew不仅仅对FPGA入门学习流程做了详细的分享,更是对FPGA开发工作的要求分成大公司和小公司两个层面来分析。你能想象曾经从一个疏忽学业的人成为一名资深FAE的嘛?

1. 您认为想学FPGA的话,先学好什么才最重要?

Andrew:我们玩FPGA的通常就是跟数字电路打交道,要想玩得转,必须先学习并掌握最最基础的数字电路和HDL硬件描述语言,当然这只是入门必备,实际上远远不够。个人拙见,要入

- 关键字:

ALTEAR FPGA FAE

- 电流互感器作为高压电网检测主要设备,不仅为电能的计量提供参数,而且是为继电保护提供动作的依据。随着国家智能电网和特高压电网的发展,传统电磁式电流互感器逐渐暴露出其致命缺陷,例如高电压等级时绝缘极为困难、更高电压下易磁饱和导致测量精度下降等。相比之下,光纤电流互感器具有抗电磁干扰能力强、绝缘可靠、测量精度高、结构简单和体积小巧等诸多优点,是当前研究热点。作为光纤电流互感器的核心部件,其检测和控制电路对电流检测精度和范围具有非常重要的影响。

目前检测和控制电路实现主要有两种方案,一种是以数字信号处理

- 关键字:

FPGA DSP 互感器

fpga soc介绍

您好,目前还没有人创建词条fpga soc!

欢迎您创建该词条,阐述对fpga soc的理解,并与今后在此搜索fpga soc的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473