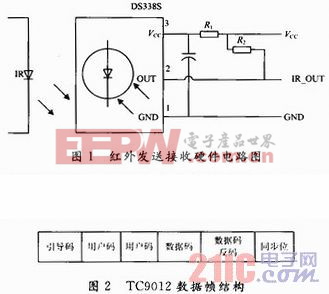

- 摘要:提出一种红外解码IP核在SoPC系统中的设计与实现方案,重点研究红外系统的数据编码和传输机制,红外解码电路的HDL设计,IP核的制作及在SoPC系统中的应用。该方案的红外发送接收芯片分别是TC9012和DS338S,在DE2

- 关键字:

设计 实现 IP 解码 SOPC 红外 基于

- 标签:IP/HD-SDI 高速球技术高清网络高速球技术分析高清网络高速球是在传统模拟高速球的基础上发展而来,在其基础上,增加高清一体化机芯、视音频编码模块、网络接入模块,即可构成一个基本的网络型高速球,实现高清

- 关键字:

趋势 探讨 发展 技术 高清 高速 IP/HD-SDI

- 1 引言DDR2(Double DataRate2)SDRAM是由JEDEC(电子设备工程联合委员会)制定的新生代内存技术标准,它与上一代DDR内存技术标准最大的不同:虽然采用 时钟的上升/下降沿同时传输数据的基本方式,但DDR2却拥有2倍的DDR

- 关键字:

Spartan Xilinx FPGA DDR2

- X-fest 2012全球系列研讨会北京站于7月10日举办,创下了单场活动吸引上千名业内人士参加的新记录。X-fest是为期一天的全球性培训活动,由安富利公司 (NYSE: AVT) 旗下安富利电子元件亚洲 (Avnet Electronics Marketing )主办,深受FPGA、ARM MCU、DSP和嵌入式系统开发人员欢迎。

- 关键字:

安富利 X-fest FPGA

- 1、控制系统概述随着工业的发展,三坐标测量机越来越显示出其重要作用。而电机控制系统对三坐标测量机的运行有着非常重要的作用。由于FPGA可以现场可编程,可以实现专用集成电路,能满足片上系统设计(SOC)的要求,使

- 关键字:

FPGA 三坐标测量机 电机控制系统

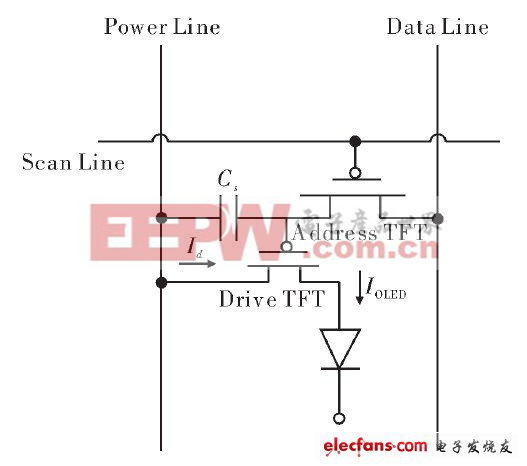

- 256 级灰度显示 - 基于FPGA的OLED真彩色显示设计,摘要利用FPGA 控制模块,设计了OLED 真彩色动态图像驱动控制电路。介绍采用FPGA 实现OLED 外围控制电路和256 级灰度的方法,并分析电路中模块的作用及整个电路的工作过程。电路系统采用基于Altera 公司的FPGA技术进行

- 关键字:

显示 彩色 设计 OLED FPGA 基于 级灰度

- 工程师分析实例,带你走近Xilinx FPGA设计,一.概述 本文主要帮助大家熟悉利用ISE进行Xilinx 公司FPGA 代码开发的基本流程。主要是帮助初学者了解和初步掌握 ISE 的使用,不需要 FPGA 的开发基础,所以对每个步骤并不进行深入的讨论。 本文介绍的内容从新

- 关键字:

FPGA 设计 Xilinx 走近 分析 实例 工程师

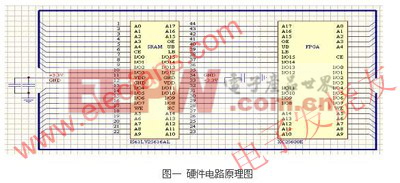

- 采用FPGA与SRAM的大容量数据存储的设计,1 前言 针对FPGA中内部BlockRAM有限的缺点,提出了将FPGA与外部SRAM相结合来改进设计的方法,并给出了部分VHDL程序。 2 硬件设计 这里将主要讨论以Xilinx公司的FPGA(XC2S600E-6fg456)和ISSI公司的SRAM(IS61LV

- 关键字:

存储 设计 数据 大容量 FPGA SRAM 采用

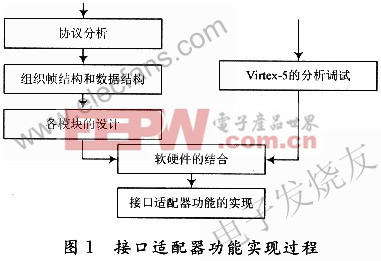

- 采用上位机与FPGA开发板的光纤通道接口适配器设计,随着存储技术的迅速发展,存储容量得到了迅速的增长,存储系统的数据传输速度成为了主要的瓶颈。光纤的传输具有其速度上的优势,然而,在光纤传输要受到光纤通道接口的限制,因此光纤通道应用于高速数据传输的一个关

- 关键字:

接口 适配器 设计 通道 光纤 上位 FPGA 开发 采用

- 利用Java良好的移植特性的FPGA可编程嵌入式系统,传统的嵌入式产品只能实现某种特定的功能,不能满足用户可变的丰富多彩的应用需求。为解决这个问题,本文设计并实现了一种使用Java作为软件平台的基于FPGA的可编程嵌入式系统,以实现系统对多种本地应用和网络的支持

- 关键字:

可编程 嵌入式 系统 FPGA 特性 Java 良好 移植 利用

- FPGA全局时钟资源相关Xilinx器件原语及使用,FPGA全局时钟资源一般使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构,从而使全局时钟到达芯片内部的所有可配置单元(CLB)、I/O单元(IOB)和选择性块RAM(Block Select RAM)的时延和抖动都为最小。为了适应复杂设

- 关键字:

Xilinx 器件 使用 相关 资源 全局 时钟 FPGA

- FPGA/EPLD的自上而下设计方法及其优缺点介绍,FPGA/EPLD的自上而下(Top-Down)设计方法: 传统的设计手段是采用原理图输入的方式进行的,如图1所示。通过调用FPGA/EPLD厂商所提供的相应物理元件库,在电路原理图中绘制所设计的系统,然后通过网表转换产生某一特

- 关键字:

缺点 介绍 及其 方法 自上而下 设计 FPGA/EPLD

- Altera公司(NASDAQ: ALTR)日前宣布,推出40-Gbps以太网(40GbE)和100-Gbps以太网(100GbE)知识产权(IP)内核产品。这些内核能够高效的构建需要大吞吐量标准以太网连接的系统,包括,芯片至光模块、芯片至芯片以及背板应用等。

- 关键字:

Altera FPGA

fpga ip介绍

您好,目前还没有人创建词条fpga ip!

欢迎您创建该词条,阐述对fpga ip的理解,并与今后在此搜索fpga ip的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473