引言

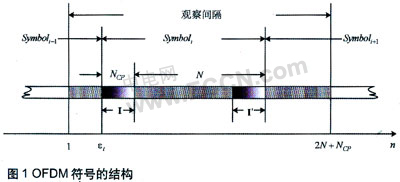

正交频分复用(OrthogonalFrequency Division Multiplexing,OFDM)技术已经成为第四代移动通信研究的热点,同时,OFDM同步又是OFDM的关键技术,研究OFDM同步技术的目的就是为了防止码间干扰和载波干扰。当前OFDM同步的算法是根据OFDM原理提出的基于数据符号方法,它的优点是捕获快、精度高,适合分组数据通信,具体的实现是在分组数据包的包头加一个专门用来做定时、频偏的OFDM块。基于数据符号的算法又可以分为两类:基于训练符号(导频码)的方法和基于循

关键字:

OFDM FPGA DSP I/O

电子产品世界,为电子工程师提供全面的电子产品信息和行业解决方案,是电子工程师的技术中心和交流中心,是电子产品的市场中心,EEPW 20年的品牌历史,是电子工程师的网络家园

关键字:

DSP 控制 三电平 变频器 异步电机

1 引 言

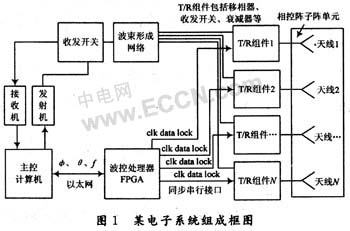

相控阵是通过波控系统控制阵列天线各单元通道的相位、幅度以形成空间波束并控制其方位角和俯仰角。早期的波控系统一般采用硬件电路来实现,这种实现方法的缺点是设备量大,不灵活,很难实现波束的复杂计算,不易满足特殊要求。后来采用单片机、DSP芯片来设计波控系统,单片机通常不计算波控码,仅仅是根据接收到的波控码布相,而DSP可以自己计算波控码,但是单片机、DSP都是象流水线一样串行的运行指令,也就是说,不能并行地对各天线单元通道进行波控码计算和布相。

针对波控系统要求高速计算、多通道并行逻

关键字:

以太网 接口 天线 FPGA

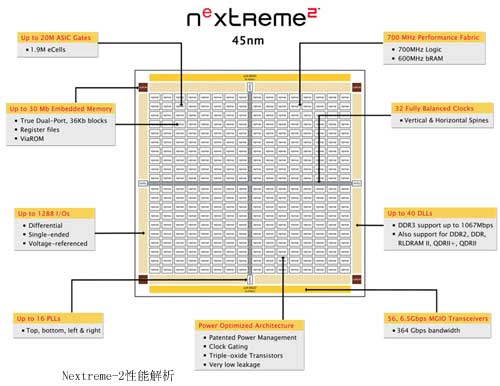

半导体调研机构Gartner多年来一直在跟踪ASIC设计项目数量,其趋势已经无疑被认定向下。最新技术的ASIC设计费用已经上升到一个很高点,以致许多中小规模的公司用不起而只能采用FPGA。而ASIC只有依靠正在研发的各种降低其设计费用的新方法才有希望挽回颓势。

拥有独特的过孔层布线定制专利技术以及零掩模费和无最低订货量限制的新结构化ASIC平台供应商eASIC在其90nm Nextreme ASIC产品的基础上,又发布了其新一代Nextreme-2系列产品。Nextreme-2系列是目前市面上唯

关键字:

ASIC FPGA 信号处理 富士通

Cirrus Logic公司日前宣布推出采用杜比音量(Dolby Volume)技术的音频DSP CS49DV8,以帮助降低电视节目里尖锐的广告声,提高用户的聆听体验。

CS49DV8是一款采用杜比音量技术的八声道、双内核、32位音频DSP,消费者可以自行设置最理想的音量水平,并使音量维持在该水平。该产品的目标应用为多声道环绕声应用,如音频/视频接收机、家庭影院组合套装应用,以及条形扬声器。为满足这些应用的需求,CS49DV8还可额外提供各种音频后处理能力,如低音管理

关键字:

CirrusLogic DSP 音频 Cirrus Logic 杜比

1 引 言

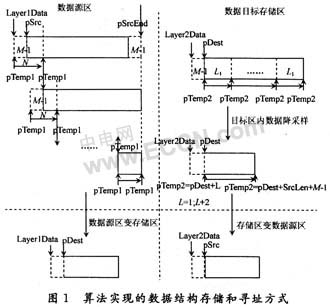

由于小波变换具有良好的时频分析特性,已经广泛应用于各种信号分析领域。由于小波变换算法的复杂性,如果直接计算小波变换,所需内存较大,耗时较长。尽管当今处理器芯片运算速度得到了大幅度的提高,但仍然在实时性上不能满足要求。为了简化计算过程,人们相继设计了一系列的快速算法来计算小波变换,以降低其运算次数。

小波变换在大多数具体应用中主要是在线信号的实时分析处理,微机和通用的微处理器在运算速度上难以适应信号实时、高精度处理的要求。数字信号处理器(DSP)就是为了适应这种需求而开发的。美国

关键字:

DSP 小波变换 微处理器 低功耗

Altera公司今天公布了其亚太区年度SOPC World大会的时间和地点。大会将于2008年10月在印度和中国的5个城市举办。

大会包括技术研讨和展览两部分,系统设计人员通过此次大会来将了解到怎样降低系统成本,并满足严格的功耗预算要求,提高效能。在技术研讨会上,Altera及其合作伙伴将为出席人员介绍最先进的高功效可编程器件以及高效能开发工具等。

关键字:

Altera FPGA SOPC

2008年9月5日,闻亭数字系统(北京)有限公司和亚嵌教育培训中心共同签署了战略合作伙伴意向书。这将意味着闻亭数字和亚嵌教育正式确立了战略合作伙伴关系,共同为DSP和嵌入式领域的客户提供更多、更优质、更深入的服务。据悉,双方将会在企业客户培训、市场推广和技术交流方面携手共进。

闻亭数字系统(北京)有限公司是DSP和嵌入式领域资深企业,在DSP领域的成就和贡献已经得到广大客户的认可;闻亭还是国内最早从事嵌入式开发研究的企业之一;作为国内最早的TI全球第三方合作伙伴,十二年来以为上千家客户提供D

关键字:

闻亭数字系统 亚嵌教育 DSP 嵌入式

目前,越来越多的FPGA设计开始采用嵌入式处理器,如PowerPC和赛灵思(Xilinx)的MicroBlaze处理器来完成控制任务,...

关键字:

FPGA 嵌入式 处理器 除错率 赛灵思

介绍了DSP与慢速设备接口的一种时序转换方法。通过该方法,可以解决DSP与传统输入输出设备时序不匹配的问题,从而实现DSP与8080、6800等时序兼容的或其它慢速读写周期的输入/输出设备的直接连接,如液晶显示模块、打印机、键盘等。这种时序转换方法能使DSP在工业控制和测试设备中获得更加广泛的应用。

关键字:

实现 接口 设备 慢速 DSP

电子产品世界,为电子工程师提供全面的电子产品信息和行业解决方案,是电子工程师的技术中心和交流中心,是电子产品的市场中心,EEPW 20年的品牌历史,是电子工程师的网络家园

关键字:

DSP FPGA FIR QuartusⅡ

2008年,以第一名的身份荣膺《电子产品世界》颁发的“2008年度中国本土嵌入式系统十佳企业”殊荣公司上A6协同系统,实现了全公司多个办事处之间,多部门之间的协同,更加规范了工作的流程。

关键字:

SEED DSP

“电子产品需求持续变化,只给制造商两条出路――Differentiate or Die (要么追求差异化,要么关门消亡!)这给可编程器件带来了巨大的发展机遇!”8月28日,年初走马上任的Xilinx总裁兼CEO Moshe Gavrielov首次接受中国媒体的采访,透露了Xilinx新的发展策略,概括起来就是三“新”:新架构、新思路、新服务。

Moshe曾经供职于NSC、LSI、Cadence等公司,从微处理器芯片、ASIC芯片、EDA软件再到可编

关键字:

处理器 EDA FPGA Xilinx PLD Moshe

1 引 言

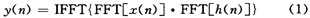

作为一种探测目标信息的工具,雷达在现代战争中发挥着举足轻重的作用。在雷达回波信号处理中,通常利用线性调频信号脉冲压缩技术来获得高的距离分辨率。他有效地解决了雷达作用距离与距离分辨率之间的矛盾,可以在保证雷达作用距离的情况下提高雷达的距离分辨力。数字脉冲压缩就是利用数字信号处理的方法来实现雷达信号的脉冲压缩,分为时域和频域两种实现方式。时域脉压常用数字滤波器实现,而频域脉压常用专用的FFT芯片或DSP完成。一般而言,对于小时宽带宽积信号,用时域脉压较好;但对于大时宽带宽积信号,用频域脉

关键字:

DSP 雷达 芯片 硬件平台

dsp+fpga介绍

您好,目前还没有人创建词条dsp+fpga!

欢迎您创建该词条,阐述对dsp+fpga的理解,并与今后在此搜索dsp+fpga的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473