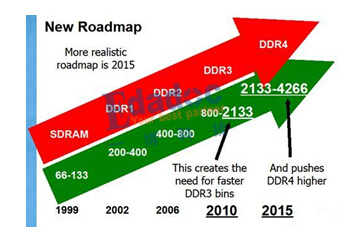

引言:DDR4 等存储技术的发展带动存储器速度与功率效率空前提升,仅仅停留在一致性测试阶段,已经不能满足日益深入的调试和评估需求。DDR 存储器的测试项目涵盖了电气特性和时序关系,由JEDEC明确定义,JEDEC 规范并

关键字:

高速存储器 一致性测试 DDR

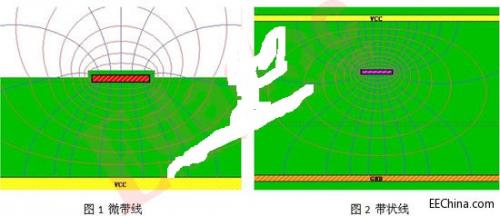

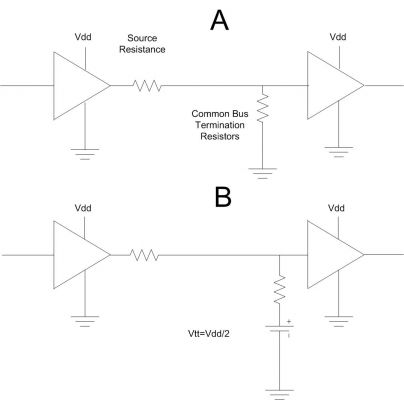

高速电路设计领域,关于布线有一种几乎是公理的认识,即“等长”走线,认为走线只要等长就一定满足时序需求,就不会存在时序问题。本文对常用高速器件的互连时序建立模型,并给出一般性的时序分析公式。为

关键字:

PCB DDR SDRAM PHY芯片

SDRAM与DDR SDRAM

SDRAM是比较久远的事情了,但我们一说到它肯定不会和 DDR混淆,我们通常理解的SDRAM其实是SDR SDRAM,为SDRAM的第一代,而DDR1则为第二代,乃至到我们现在使用的DDR4,其实为第五代SDRAM,在此需要澄清一下。以示区别,后续文 章里面用SDR来特指SDR SDRAM,而DDR就特指DDR SDRAM了。

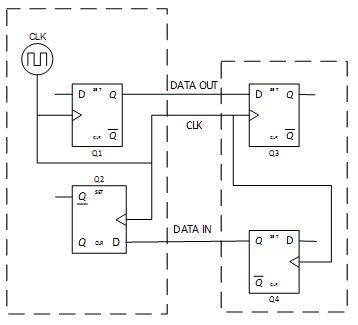

就像很多人回复的一样,他们的本质区别就是周期操作方 式(也称时钟采样)的差异,这就导致后面设计上很大的不同。SDR都是“

关键字:

DDR SDRAM

混合信号半导体解决方案供应商 IDT® 公司宣布支持基于 Nehalem 的 Intel® Xeon® 处理器,该处理器采用可进行生产的 PCI Express®(PCIe®)交换和计

关键字:

IDT DDR

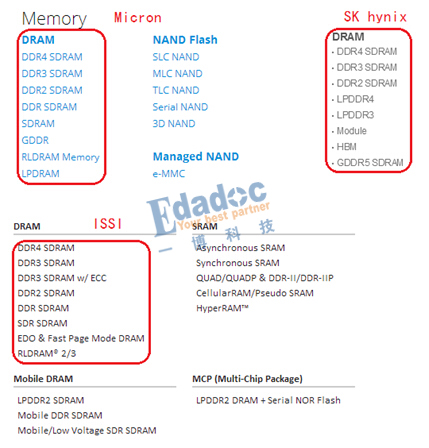

射频功率、成像和高可靠性半导体解决方案领域的领军企业 e2v aerospace and defense, Inc. (e2v ad) 近日宣布,将延长世界领先高级存储解决方案供应商之一 Mic

关键字:

Micron e2v DDR

DDR SDRAM全称为Double Data Rate SDRAM,中文名为“双倍数据率SDRAM”。DDR是在原有的SDRAM的基础上改进而来,严格的说DDR应该叫DDR SDRAM,人们习惯称为DDR。

说到这里,很多人可能会问SDRAM、DRAM、SRAM或者RAM、ROM到底是什么鬼,怎么区别的?小编还是来简单普及下关于存储的基础知识吧。

ROM 和RAM指的都是半导体存储器,ROM是只读存储器(Read-Only Memory)的简称,是一种只能读出事先

关键字:

DDR DRAM

新思科技(Synopsys, Inc.)日前宣布:推出全新的DesignWare® USB-C 3.1/DisplayPort 1.3知识产权(IP)解决方案,该解决方案集成了USB Type-C™(USB-C™)、SuperSpeed USB 10 Gbps(USB 3.1 Gen 2)和DisplayPort 1.3接口,以及带有高带宽数字内容保护(HDCP)2.2 I

关键字:

Synopsys DesignWare

信号在媒质中传播时,其传播速度受信号载体以及周围媒质属性决定。在PCB(印刷电路板)中信号的传输速度就与板材DK(介电常数),信号模式,信号线与信号线间耦合以及绕线方式等有关。随着PCB走线信号速率越来越高,对时序要求较高的源同步信号的时序裕量越来越少,因此在PCB设计阶段准确知道PCB走线对信号时延的影响变的尤为重要。本文基于仿真分析DK,串扰,过孔,蛇形绕线等因素对信号时延的影响。

1.引言

信号要能正常工作都必须满足一定的时序要求,随着信号速率升高,数字信号的发展经历了从共同步时钟到

关键字:

PCB DDR

是德科技公司日前在 DesignCon 2015 展会上展示其高速数字解决方案。本届展会于 1 月 28 日到 29 日在美国加州圣克拉拉会展中心举行,是德科技展位设于第 725 号展台。是德科技非常自豪能够接替其前身惠普公司和安捷伦公司,继续担任 DesignCon 展会的发起方和主办方。一年一度的 DesignCon 展会即将迎来其 20 周年纪念日。作为主要面向高速通信和半导体行业中的芯片、电路板和系统设计工程师的一项活动,它已成为行业中最重要的展会。

是德科技将展出众多仿真、建模、测试和

关键字:

是德科技 DDR

Memory是系统运行和性能的核心。设计人员需要更好地了解内存子系统,以优化系统吞吐能力。

如今Memory炙手可热。最近在加利福尼亚州举行的2014 MemCon盛况空前,展厅里展示了几乎所有关于Memory的产品,参会的人也热情高涨。

会议主题是,是否有更为行之有效的方法来特性化分析DDR Memory的系统裕量。尤其是DDR子系统(DDR controller, PHY和 I/O))被嵌入到芯片用于承担处理器和外部DDR存储器之间的数据交互任务,这使得这种分析变得更加困难。 要知道,

关键字:

MEMCON Memory DDR-SDRAM

弹性客制化IC设计领导厂商(Flexible ASIC Leader™)创意电子(Global Unichip Corp.,GUC)与高度创新的fabless Soc – centric IC芯片设计公司, 信骅科技(ASPEED Technology, Inc.)采用业界第一个以台积电公司40nm低功耗(Low Power,LP)工艺节点的DDR3/4 PHY,大幅加速了一远程管理控制器的系统设计, 此控制器用于服务器及桌面虚拟化。

创意电子的DDR 3/4 PHY为业

关键字:

创意电子 ASIC DDR

加速芯片和电子系统创新而提供软件、知识产权(IP)及服务的全球性领先供应商新思科技公司(Synopsys, Inc.,纳斯达克股票市场代码:SNPS)日前宣布:其用于高压工艺的DesignWare AEON Trim NVM IP开始供货。与其它的NVM IP解决方案相比,该款全新的IP将面积缩小达75%,同时有助于降低汽车IC的成本和尺寸。该IP可用于标准的180纳米5V CMOS和BCD工艺,而不需要额外的光罩或工艺步骤。DesignWare NVM IP支持Grade 0汽车应用所需要的宽温度范围,

关键字:

Synopsys DesignWare AEC-Q100

新思科技公司(Synopsys, Inc)日前宣布:其多协议DesignWare® Enterprise 12G PHY IP正式上市,该物理层知识产权(PHY IP)将使多样化的高端网络和计算应用在功耗降低的同时提升了性能。DesignWare Enterprise 12G PHY是专门为应对设计师们所面临的不断增长的性能/功耗平衡挑战而设计,它使设计师能够轻松地将各种企业级通信协议集成到他们的系统级芯片(SoC)上,包括PCI Express 3.0、SATA 6G、10GBASE-KR、10GB

关键字:

Synopsys DesignWare

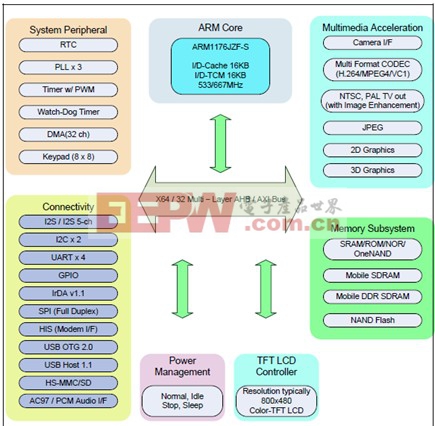

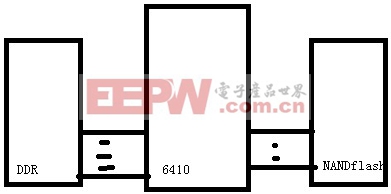

当在S3C6410跑操作系统的时候,我们不太会注意S3C6410的内存使用情况,但是,当我们做裸板测试时,该处理器的8K的片内内存的使用就不得不注意,一旦编写的程序大小超过了片内内存的大小,我们就不能得到正确的结果,究其原因,我们先看一下S3C6410的启动过程。

关键字:

ARM11 DDR NANDflash 内存

designware ddr介绍

您好,目前还没有人创建词条designware ddr!

欢迎您创建该词条,阐述对designware ddr的理解,并与今后在此搜索designware ddr的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473