Xilinx的CEO Moshe Gavrielov在接受电子周刊的独家系列釆访时,谈到从过去的12个月到未来semi工业面临的挑战与机会。

从2009年开始过去半导体工业的那种类推模式的发展已不能适用于目前的半导体公司及未来的全球电子市场的生存需要。

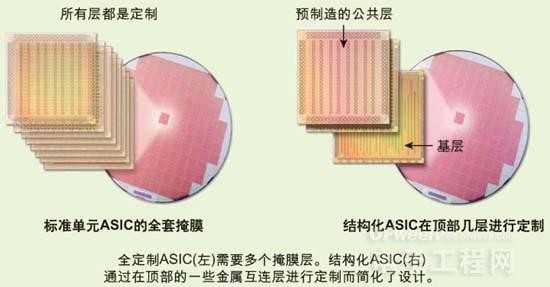

此次经济的下降周期加速了技术与贸易挑战,同时由于产品可移动性和无限连结的市场需求,使得产品设计的复杂性和风险度提高。所以要求设计公司必须提高产品进入市场的精准度,严格控制成本开支,尤其是在ASIC和ASSP电路设计中必须重视的工程费用的不断

关键字:

Xilinx 半导体 ASIC

世界领先的纯晶圆代工厂之一,上海华虹NEC电子有限公司(以下简称“华虹NEC”)日前宣布成功推出nvSOC产品原型平台,这一平台的推出可以帮助客户高效创建SOC和ASIC原型,大大缩短客户SOC产品开发周期和减少设计风险。

nvSOC平台的硬件主要由通用FPGA芯片和华虹NEC特有的平台核心IP芯片构成,其中平台核心IP芯片是指集成了华虹NEC 某一种NVM(Non Volatile Memory, 包括Flash,EEPROM,OTP等)工艺平台的NVM模块和基础模拟/

关键字:

华虹NEC 晶圆代工 SOC ASIC

随着我国教育科研网(CERNET)的不断普及和推广使用,许多高等学校将远程网络教育作为辅助教学的一个重要手段。网络教育的基础是建立网络教室系统,其中,传统的黑板被电子白板所替代,电子白板不仅可以满足教师的需

关键字:

设计 系统 电子白板 IP 基于

电子产品世界,为电子工程师提供全面的电子产品信息和行业解决方案,是电子工程师的技术中心和交流中心,是电子产品的市场中心,EEPW 20年的品牌历史,是电子工程师的网络家园

关键字:

IP 一体化呼叫中心 网络结构

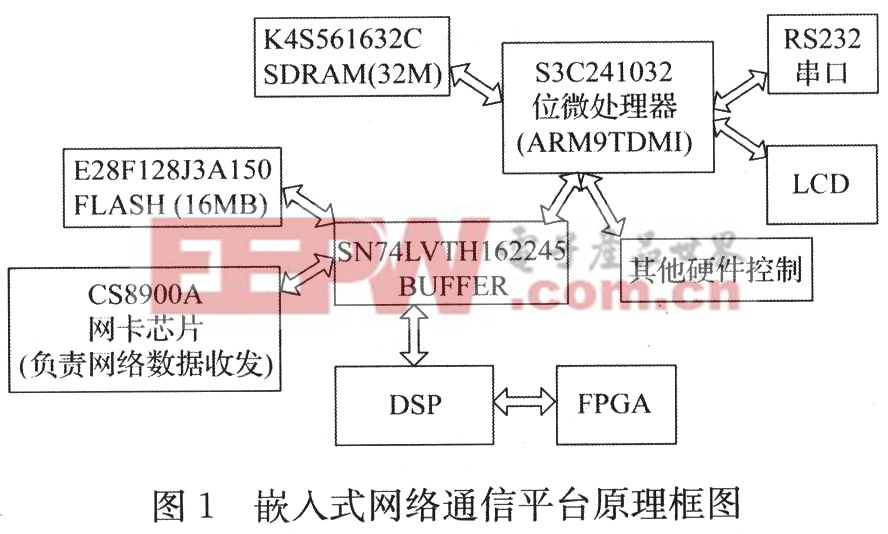

基于ARM微处理器TCP/IP协议栈LwlP实现,0 引 言

关键字:

协议 LwlP 实现 IP TCP ARM 微处理器 基于

IP over SDH(PoS)技术是通过SDH提供的高速传输通道直接传送IP分组,它位于数据传输骨干网,使用点到点协议PPP将IP数据包映射到SDH帧上,按各次群相应的线速率进行连续传输,其网络主要由大容量的高端路由器经由高速光

关键字:

ASIC FPGA IPv6 PoS

引 言

关键字:

FPGA 8051 OC IP

据国外媒体报道,美国市场研究公司Gartner表示,全球半导体创业公司今年以来总计筹集了超过7.5亿美元资金,但其中约四分之一的投资来自于大型半导体公司旗下风投部门等战略投资者。

Gartner指出,在过去的这一年,风投公司主要青睐投资后期创业公司,与去年相比,今年获得投资的创业公司数量明显下降。每家公司获得的投资金额最高为4000万美元,平均为1430万美元。

Gartner表示,在获得投资的创业公司中,70%为无晶圆厂芯片公司,14%为EDA(电子设计自动化)公司,7%为IP公司,5%

关键字:

半导体 IP OEM

随着集成电路设计技术和深亚微米制造技术的发展,集成电路已进入了片上系统时代。由于SoC结构极其复杂,对于设计者而言,数百万门规模的系统级芯片设计不可能一切从头开始,随着集成电路设计技术的发展,IP核的

关键字:

模块 设计 IP 音频 SoC 基于 音频

首先分析Chirp函数在频域上的一般特性,并且分析Altrea公司提供的数控振荡器知识产权核(NCO IP core)的输入/输出特性,通过MegaCore环境确定其输入控制字,通过外围逻辑电路实时向NCO IP core调入控制频率控制字以达到改变输出频率的目的,并通过在示波器上观测FPGA的运行情况,验证了该设计具有很好的输出效果。

关键字:

Chirp core NCO IP

针对IC前端设计中的关键技术,即将寄存器传输级(RTL)描述的手工综合成门级网表,通过人工参与的方式,运用数字电路设计知识将行为级代码用一些最基本的逻辑门(比如与非门、非门、或非门等)按照时应的综合电路模型得出其相应的门级电路。在ASIC设计过程中运用这种方法,不仅优化电路的结构,且能保证逻辑功能的正确性,同时可降低传输过程中的延迟,提高芯片设计的可靠性。因此,研究ASCI设计中的手工综合具有重要的实用价值。

关键字:

ASIC

Altera 公司 宣布推出业界首款支持 RapidIO® 2.1 规范的知识产权 (IP) 内核。Altera 的串行 RapidIO IP 内核可支持多达四条通道,每条通道速率为 5.0 GBaud,从而满足了无线市场日益增长的带宽和可靠性需求。该

关键字:

RapidIO Altera 2.1 IP

Avago Technologies(安华高科技)今日宣布,公司提供的关键知识产权(IP, Intellectual Property)已经帮助Juniper Networks公司成功进行高性能硅芯片器件产品的开发,这些新设计为带来Juniper公司MX-3D平台Junos® Trio芯片组的一部分。Avago为提供通信、工业和消费性等应用模拟接口元器件之全球领导厂商。

每个器件都拥有接近100个SerDes串行/解串器通道,并且可以推动松散背板通道和多重背板连接器,除了展现出同级产品最

关键字:

Avago 硅芯片 IP

Open-Silicon、业界标准处理器架构与内核领导厂商 MIPS 科技公司和Virage Logic 三家公司共同宣布,已成功开发一款测试芯片,充分展现出构建高性能处理器系统的业界领先技术。该处理器测试芯片实现了1.1GHz的频率速度,成功通过了65nm 芯片测试,使其成为65nm ASIC 中最快的处理器之一。同时,后续40nm器件的开发工作也已经开始进行,目标是超过2.5GHz频率,并提供超过5000 DMIPS的性能。这项开发计划采用了Open-Silicon的CoreMAXTM技术,以及超

关键字:

MIPS ASIC 测试芯片 65nm 40nm

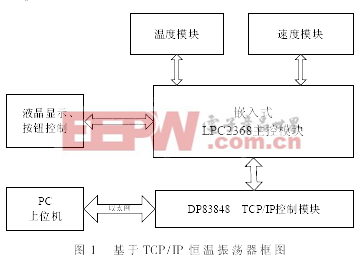

嵌入式TCP/IP技术在恒温振荡器中的应用,介绍了一种基于嵌入式TCP/IP技术的恒温振荡器的数据传输系统,使TCP/IP技术应用于恒温振荡器的设计,实现远程监控的功能。给出了恒温振荡器温度和速度控制等关键技术的实现方法。

关键字:

振荡器 应用 恒温 技术 TCP/IP 嵌入式 转换器

asic ip介绍

您好,目前还没有人创建词条asic ip!

欢迎您创建该词条,阐述对asic ip的理解,并与今后在此搜索asic ip的朋友们分享。

创建词条

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473