采用MPC5200实现高速视频探测的车内应用

汽车厂商正越来越多地通过对车内和车外捕捉到的高速视频影像进行处理来提高汽车的安全性。举例来说,安装在车内的摄像机可用于确定乘客在车内的位置,从而以最佳方式配置气囊并避免乘客受到伤害。安装在车内不同位置的摄像机还可以用于车道偏离监测、碰撞前警示、避免碰撞、后倒车灯警示和车距计算等。这些应用中有很多需要以非常高的速率来捕捉视频影像。相应地,视频影像必须通过实时的复杂算法进行处理,从而为车内的安全控制系统提供反馈。这是一项非常重要的任务,它可以避免发生碰撞,或在车辆发生碰撞的瞬间决定车内乘客的位置。而且,该项技术要要求司机侧的引擎绝热板必须能承受最高85℃的高温,而在车内的其它部位则需要承受最高达105℃的高温。

当前,汽车厂商们面临的挑战是拥有一种具备如下特征的经济高效的技术:

支持连接CMOS视频传感器的标准化高速接口

强大的处理能力

充足的MIPS,在需要时可执行视频探测算法

双倍精度的浮点单元(FPU),可提高执行算法的速度

读取全部图像的DMA能力

减少中断的次数,提高整体数据吞吐量

加快高速存储系统的访问速度

将处理器核心从处理日常数据移动功能中解放出来

支持下一代双数据速率(DDR)内存,实现快速数据存储和检索

与安全设备(如气囊等)实现经济高效的快速连接

集成的CAN和J1850 BD C可以降低数据传输的延迟和总体系统成本

可扩展到下一代汽车网络,如面向媒体的系统传输(MOST®)

能在85℃和105℃环境中运行,具体视成像传感器所处的位置而定

只需较低功率即可运行

DDR内存

CMOS成像传感器

来自于飞思卡尔半导体公司(前身为摩托罗拉)的MPC5200高性能嵌入式处理器以一个紧凑型的低功率设备就能满足所有这些设计要求。

尤其值得一提的是,MPC5200集成了一个高性能的MPC603e核心,该核心能在400 MHz 的频率和-40至85℃的温度范围内处理760 Dhrystone 2.1 MIPS。PowerPC® 核心也利用了一个高性能、双倍精度的浮点单元(FPU),可加快与其它关键任务平行的复杂数学运算的速度。以264 MHz (500 MIPS)运行的105 ℃版本还可以用于司机座位以外可能需要更高温度级别的地方。

在FPU的帮助下,MPC5200处理能力可为大多数视频探测算法提供足够的支持。集成的PCI接口则为CMOS图像传感器提供标准化的高速接口。CMOS图像传感器能以每秒80至100帧的速率将图像数据传输到MPC5200中,具体视PCI时钟和照片的分辨率而定。

BestComm智能DMA控制器能加快摄像机数据传输到内存中进行处理的速度,从而最大程度地减轻MPC603e主处理器核心上的负荷,使其可以解放出来,处理视频探测算法等任务。此外,BestComm控制器的使用还可以最大程度地降低主核心上的总体中断负荷,继而加速总体吞吐量。集成的CAN和J1850控制器,再加上外置MOST® 的支持,为汽车安全系统的剩余部分提供了经济高效的集成,并降低了与这些网络进行通信的延迟。

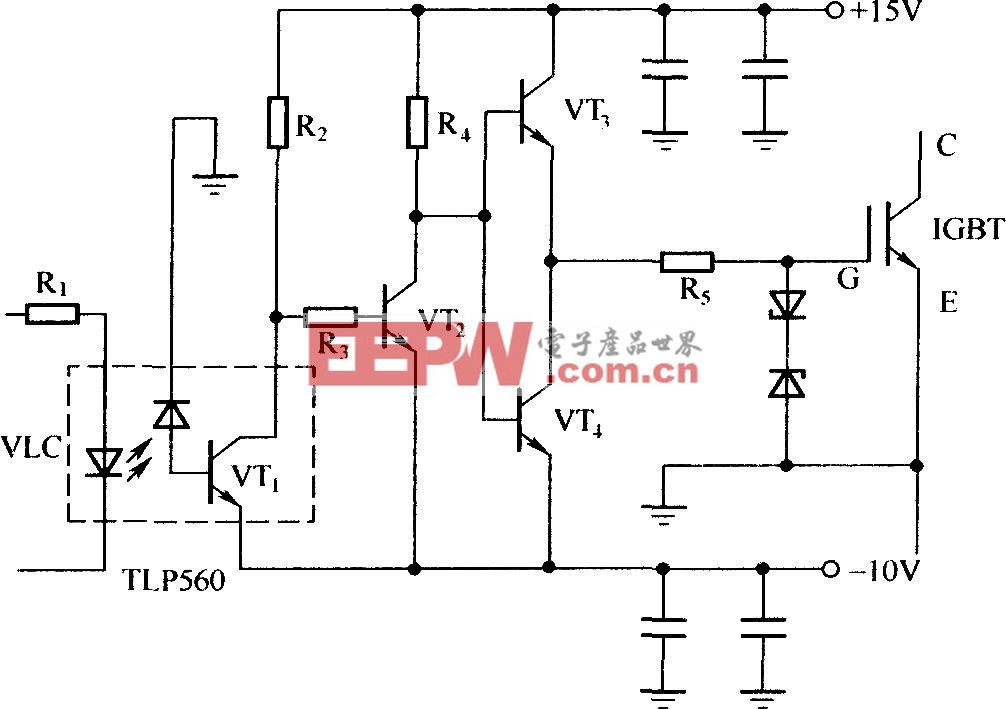

下文描述了如何通过PCI接口,为MPC5200设计一个基本的高速摄像机接口电路。在本例中,我们使用了飞思卡尔(前身为摩托罗拉)MCM20014 CMOS传感器,但其它传感器可以使用几乎完全相同的接口机制。

该接口非常明了,而且只需较少的接口逻辑就能完成连接。

使用MPC5200的时钟假设

最可能的X B释放目标频率为132 MHz;IPBus为66 MHz;PCIc k(外部总线时钟)为66 MHz;XTA 的预期输入频率为33 MHz。

对于本应用,最大的PCI频率为33 MHz。

时钟选择代表如下可能的4-1、2-1或1-1比率结构:X B->IPBus、IPBus->PCIc k。在132 MHz X B时,IPBus必须设置为4:1或2:1(分别适用于33 MHz 或66 MHz IPBus)。根据IPBus 的情况(33 MHz、16.5 MHz与 33 MHz IPBus一起工作;或33 MHz 与a 66 MHz IPBus一起工作),PCIc k可能支持1:1的比率,也可能支持2:1的比率。在处理器端,可能使用一个66 MHz的PCIc k ,但在撰写本文时,市场上的图像传感器还未达到该速度。

如果要求50%的负载循环,生成HC K的PWM输出值只能是IPBus时钟的偶整数商。

注释

从BestComm 到X B的突发处理在XB 频率上进行处理,但来自外围设备的数据由BestComm在IPBus频率上捕捉。

可能的时钟关系示例:

XTA :27 MHz,X B:108 MHz,IPB:54 MHz, PCI:27 MHz,HC K:13.5 MHz (来自 IPBus时钟的4/1比率的PWM)

XTA :33 MHz, X B:132 MHz, IPB: 66 MHz, PCI:33 MHz, HC K:8.25 MHz (来自 IPBus时钟的8/1比率的PWM)

XTA 输入可以变化,以产生不同的运行频率,但是8.25 MHz 的HC K应该适用于摄像机,而且它还在DMA时钟和传感器数据速率(PCIc k 到HC K)之间提供4:1的差异。这对可能发生的潜在带宽问题有所帮助。

方法是在传感器数据总线和PCI数据总线之间提供接口逻辑。我们为2:1和4:1两种情况提供了示例电路。MPC5200的接口逻辑非常简单,然而,这里有一些必须认真考虑的系统应用问题。

其中一个值得注意的事项就是,是否将PCI总线用于摄像机数据传输以外的其它用途。如果需要与其它设备共享PCI总线,接口逻辑就必须与其它PCI目标共存,这就要求有额外的电路。如果不需要与其它任何设备共享PCI总线,接口逻辑就可以认为任何PCI处理都是针对它的,这样逻辑就变得非常简单。

下面的框图中展示了连接到必需的接口逻辑或直接连接到传感器的MPC520 PCI信号。

图2中的粗线表示三态的情形。总线需要外部上拉电阻,这样在其输入值中,接口逻辑就会出现一个逻辑数字“1”。

传感器在其帧有效时段中显示:传感器上有一帧正准备进行传输。该信号将通过IRQ线连接到MPC5200。帧传输需要由MPC5200 PCI控制器驱动。

MPC5200 PCI使Frame_b输出低电平,以开始进行处理。AD线由MPC5200通过地址信息进行驱动。接口逻辑可以忽略这一阶段。

MPC5200 PCI 使Irdy_b输出低电平,以启动数据阶段。AD线仍然由MPC5200推动,直到目标(接口逻辑)判断Devse _b “要求”该处理。

注释

如果HC K与PCIc k 的比率为2:1,则PCIc k与接口逻辑的连接就没有必要(逻辑将完全变成联合体)。对一个4:1 PCIc k-HC K的比率来说(人们更期望这样),需要一个触发器来延迟和缩短PCI信号Trdy_b的持续。

只要目标保持Trdy_b处于高状态,MPC5200 PCI就能使AD总线处于三态之一(tri-state),并保持在等待状态。

在任何刚出现的PCIc k边缘,其中Trdy_b被探测为低,PCI就会捕捉到数据并认为要传输一个数据拍。

在完成了下一个到最后一个数据拍后,MPC5200 PCI使Frame_b输出低电平,这表示正在请求最后一个数据拍。

当目标传输完最后一个数据拍(以Trdy_b变低为标志)后,MPC5200 PCI使Irdy_b输出低电平,处理完毕。

还有其它一些信号与PCI处理有关,但它们用于PCI传输的错误情况中,在本应用中不作要求。

当兼容3.3伏的CMOS摄像机传感器三态其数据总线时,传感器的数据线路就与PCI AD总线进行直接、有效的连接。否则,在这一设计中需要数据转发器。在对传感器的 ineVa id信号进行判断时,该传感器只应该驱动数据线路。

只有在没有其它真正的PCI目标设备连接到PCI接口上时,该示例接口才发挥作用。否则,某些支持的类型需要通知接口逻辑响应即将到来的PCI处理。

在2:1的情况中,当HC K低时,传感器数据有效,并随HC K的再次出现而作为下一个数据拍,下一个出现的PCIc k 边缘就会捕捉数据。

注释

PCI处理必须在 ineVa id判断之前进行。PCI处理在 ineVa id 变高时,一直由Trdy_b 保持等待状态。由于5200Enab e 要求拒绝几次循环,在PCI处理结束时可能还需要额外的电路来关闭此电路。在这一过程中,人们可能会要求进行非摄像机的PCI处理(该接口逻辑绝不能响应)。

由于HC K源自MPC5200 PWM,HC K处理发生在PCIc k边缘后(根据设计,PCIc k应提前到达总线)

当HC K下降时,Trdy_b的判断要延迟一个PCIc k

当HC K升高时,Trdy_b也立刻升高。

这在PCIc k 边缘创建了PCI数据拍捕捉,然后,PCIc k边缘再创建不断上升的HC K(其中像素在增加)

控制传感器数据读取的BestComm任务非常灵活,能根据传感器的大小进行调节。

在基于飞思卡尔(前身为摩托罗拉)CMOS传感器的本例中,我们使用640 * 480像素,每像素10比特。在每一行后面,脉冲停止,BestComm任务会自动开始下一行的读取,直到完成整幅图片。

这种方法具有很高的帧速率,每行的开销为15 c ks。

640像素数据时钟 + 15时钟= 655时钟

655 时钟 * 480 线路 = 每帧314.4k时钟

33 MHz PCI 时钟 -> 每帧9,52 ms ,每秒105帧

帧速率取决于时钟和传感器的分辨率。

为完成一幅完整的图片而读取的脉冲的长度和行数就是BestComm的参数,这些参数可以根据每种传感器的类型进行调整。

采用接口实现的帧吞吐量比该应用的帧速率要高得多。限制因素是用于算法所需的计算能力,该算法与应用的关系非常紧密。飞思卡尔(前身为摩托罗拉)能以一个集成的FPU提供400 MHz和760 MIPS的MPC603e核心。

评论