8051 与 AndesCoreTM 的软件差异与移植

5. 中断向量及异常处理函数例子

本文引用地址:https://www.eepw.com.cn/article/277992.htm以中断向量及中断处理函数的例子说明差异及移植。

5.1. 汇编实现中段向量表

[8051]

该例子显示怎样用汇编设置 8051 的中断向量和中断处理函数,在 8051 汇编 中 ORG 指定了后面汇编代码的位置,后面的中断向量通常是一个跳转语句。如 下例第一个向量跳到主函数 MAIN 函数中,另外一个外部中断 1,也是一个跳转指 令:LJMP INT 到后面的用汇编实现的中断处理函数 INT 中。

| ORG 0000H /*起始地址*/ LJMP MAIN /*跳转到主程序*/ ORG 0013H /*外部中断 1 的地址 LJMP INT /*跳转到 INT 执行*/ ORG 0100H /*主程序的起始地址 MAIN: MOV A,#0FEH /*将 FEH 送给 A*/ SETB IT1 /*外部中断 1 跳变沿触发方式*/ SETB EX1 /*外部中断 1 开中断*/ SETB EA /*CPU 开中断*/ MOV P0,A /*将 A 送给 P0*/ LOP: LJMP LOP /*循环等待*/ INT: RL A /*A 循环左移*/ MOV P0,A /*将 A 的数值送给 P0*/ RETI /*中断返回*/ END /*程序结束*/ |

[AndesCore™]

该例子显示怎样用汇编设置 AndesCore™的中断向量表和中断处理函数,该 例子中 exception_vector 是中断向量表的 label, 后面分别表示第 0,1,2,3…个中 断向量,它们只是简单的跳转指令,跳到具体的执行实体中去,如 vector 0 跳到_start,做系统相关的初始化操作,_start 是系统启动代码,用汇编语言来实现。vector 9 后面对应的是外部中断,中断处理函数如 OS_Trap_Interrupt_HW0, OS_Trap_Interrupt_HW1… 它通常用 C 来实现,可以参考后面 5.2 章节的 AndesCore™中断处理函数范例。

| ! 中断向量表所在的 section,该 section 在链接后会被存放在第一条指令 执行处,通常是 0 位置 .section .vector, "ax" !==================================================== ! Vector table !==================================================== .align 3 exception_vector: ! 以下是中断向量表 j _start ! (0) Trap Reset j OS_Trap_TLB_Fill ! (1) Trap TLB fill j OS_Trap_PTE_Not_Present ! (2) Trap PTE not present j OS_Trap_TLB_Misc ! (3) Trap TLB misc j OS_Trap_TLB_VLPT_Miss ! (4) Trap TLB VLPT miss j OS_Trap_Machine_Error ! (5) Trap Machine error j OS_Trap_Debug_Related ! (6) Trap Debug related j OS_Trap_General_Exception ! (7) Trap General exception j OS_Trap_Syscall ! (8) Syscall j OS_Trap_Interrupt_HW0 ! (9) Interrupt HW0 j OS_Trap_Interrupt_HW1 ! (10) Interrupt HW1 ....... ....... ....... ! _start 函数,是中断向量 0 对应的中断处理函数 .align 2 _start: ! ******** Begin of do-not-modify ************ ! Please don’t modify this code ! Initialize the registers used by the compiler #ifndef CONFIG_NO_NDS32_EXT_EX9 ! make sure the instruction before setting ITB ! will not be optimized with ex9 .no_ex9_begin ! disable ex9 generation #endif ! Support Relax, Set $gp to _SDA_BASE_ la $gp, _SDA_BASE_ ! init GP for small data access #ifndef CONFIG_NO_NDS32_EXT_EX9 ! Initialize the table base of EX9 instruction la $r0, _ITB_BASE_ ! init ITB mtusr $r0, $ITB .no_ex9_end #endif !*********** End of do-not-modify************ la $fp, _FP_BASE_ ! init $fp la $sp, _stack ! init $sp 初始化堆栈寄存器 #ifdef CFG_LLINIT bal _nds32_init_mem ! 初始化 DRAM #endif bal __init ! 初始化 CPU,SoC,C 运行环境等 bal main ! 最后跳转到 main 函数 1: b 1b |

在上面用汇编设置 AndesCore™的中断向量表的例子中,我们需要将中断向量表最终设定在 0 地址处,可以通过 section 语法配合 sag 工具实现,例子中我们设定 该段 的 section 名为 .vector, 所 以在 sag 中 ,我 们自 定义一个 USER_SECTION 为.vector,并将.vector 放在 0 开始的地方并作为第一个 section。

| USER_SECTIONS .vector SDRAM 0x00000000 0x00800000 ; address base 0x00000000, max_size=8M ;指定 LMA 为从 0 开始 { EXEC 0x00000000 ;指定 VMA 为 0 { * (.vector) ;放在 0 开始的地方并作为第一个 section * (+RO,+RW,+ZI) STACK = 0x00800000 } } |

通过上面的 sag 语法,并使用 andes 提供的 sag 转 ld 的工具,可以产生类似以下的 ld,在工程进行链接的时候选择该 ld 时就能确保 .vector 链接的地址位 于 0 处。

| /* This file is generated by nds_ldsag (version 20140127). */ ENTRY(_start) SECTIONS { PROVIDE (__executable_start = 0x00000000); NDS_SAG_LMA = 0x00000000 ; SDRAM_BEGIN = NDS_SAG_LMA; . = 0x00000000; ; 起始地址为 0 .vector : { *(.vector) } ; .vector 在 0 开始的位置 .nds32_init : { KEEP(*(.nds32_init)) } .interp : { *(.interp) } .hash : { *(.hash) } .dynsym : { *(.dynsym) } .dynstr : { *(.dynstr) } .gnu.version : { *(.gnu.version) } ...... |

关于详细的 SAG 使用,可以参考我们的另一篇文章:《Andes 的分散聚合(SAG)机制》http://www.andestech.com/cn/news-events/technical-article/2014/Andes20141008.pdf

5.2. 中断处理函数的 C 实现

[8051]

怎样用 C 写 8051 的中断处理函数范例

| /* com interrupt handler */ void com_int(void) interrupt 4 // 有指定 interrupt 号 { /* com interrupt handler here */ } |

[AndesCore™]

怎样用 C 写 AndesCore™的中断处理函数范例

| void syscall_handler() // 和普通函数的写法相同 { puts("this is syscall handlern"); } |

6. 适用于 MCU 的 Andes CPUs

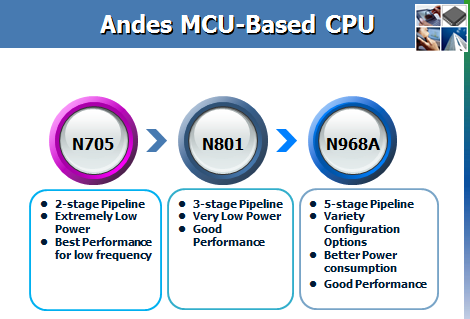

Andes 有三款非常适用于 MCU 应用的 CPU,分别是:N705,N801,N968A,如 下图所列:

N705 和 N801 分别采用了两级和三级流水线,都具有很低的功耗和很好的性 能,当应用需要的频率较低时,使用两级流水线的 N705 能发挥出更好的性能和 更低功耗的特性,相比于 8051,两级流水线的 N705 在频率方面高出许多,比 如在 TSMC 40nm LP 工艺下能跑到超过 240MHz,所以完全能胜任 8051 的应 用需求。N968A 使用了五级的流水线,同样有低功耗的特性和很好的性能,同 时该款 CPU 具有很强的可配置性,如支持多种总线接口,还支持了专门为 audio 的加速指令,N968A 是一个多面手,性能好,功耗低,又具备强大的可配置特 性,适合于多种应用。

7. 总结

AndesCore™使用标准的 C 语法开发,方便快捷,同时作为 32 位 RISC(精 简指令集)架构的 CPU,AndesCore™有多款适用于 MCU 应用的 CPU,相对于8051 具有功耗,性能方面优势。想了解更多 AndesCore™细节,可以登陆www.andestech.com。

存储器相关文章:存储器原理

评论