解析高速ADC和DAC与FPGA的配合使用

通常情况下,这些数字接口采用的是并行LVDS总线,这样它们会占用许多的FPGA I/O管脚,但是,并行接口的延迟最小,并且由于它们使用差分信号传递方式,也可以降低辐射噪声,这在高性能系统中是非常重要的。

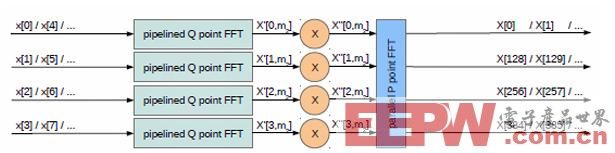

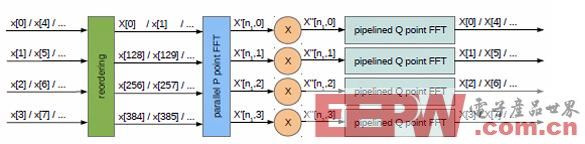

本文引用地址:https://www.eepw.com.cn/article/256789.htm收到FPGA发出的4个数据流,你可能想知道在FPGA内部是如何处理数据的,在许多应用中,包括通信处理器和射电天文,都使用的一个常用的方法是使用组合或者分离的FFT结构,如下面两个图所示:

使用4个128点的FFT流水线,加上旋转因子和1个并行4点FFT,组合成512点的FFT

分离512点FFT,与组合FFT相反。与组合FFT不同的是,在前两个阶段,对高速输入有一个重组的操作

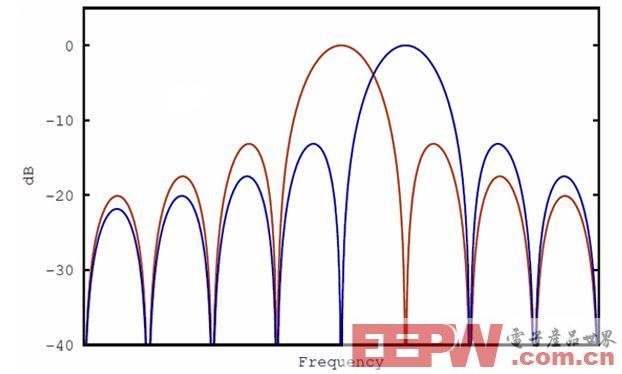

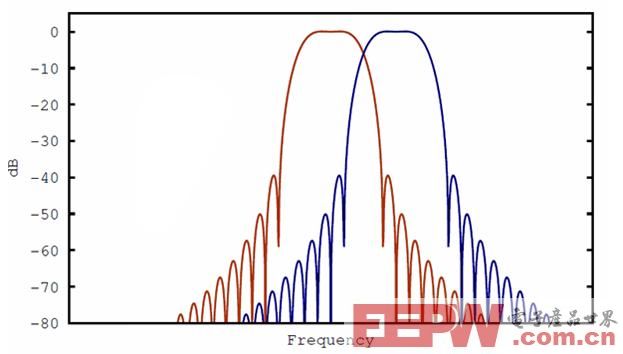

因为这些真实的数据样本,你将需要寻找一个优化的方法以便于在FFT结构中对这些数据进行处理,高效的、大FFT的实现是一个复杂的研究领域,但是在FFT之前,许多应用使用加权叠接相加(WOLA)结构来改善频谱泄漏。下面两个图显示了使用一个矩形窗口的普通FFT和使用WOLA的FFT的行为对比:

使用普通FFT矩形窗口的相邻信道

使用WOLA方法的相邻信道,显示了更少的频谱泄漏

然后,根据应用的需求,对这些合成的FFT数据进行后处理。

fpga相关文章:fpga是什么

评论