一种DSP内嵌DARAM的电路设计与ADvance MS仿真验证

存储阵列的结构如图10。存储单元为常用的6管SRAM单元,进行读写操作时,OE由低变高,预充电管关闭,通过读写放大器对位线的充电与放电来实现数据读写。

本文引用地址:https://www.eepw.com.cn/article/255835.htm3 仿真验证

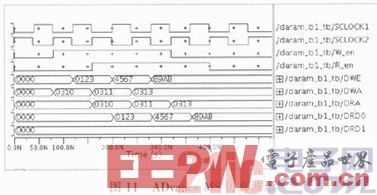

为了使仿真结果准确,输入波形应该与实际情况一致,先用ModelSim对整体DSP芯片进行仿真,然后观察DARAM的输入端,按照所得的输入信号再单独对DARAM进行仿真,由于电路中既有数字电路也有模拟电路,所以采用数模混合仿真的方法,用ADvance MS对该电路进行仿真。仿真波形如图11。

在4个时钟周期内,对DARAM进行三次写操作和三次读操作,数据在SCLOCK2上升沿时写入,在SCLOCK1上升沿时读出,在第二个周期与第三个周期内,W_en和R_en同时使能,也就是要在一个周期内进行两次操作,进行“双存取”。从两块存储阵列中读出的数据分別为DRD0和DRD1,可以看出,DRD0依次读出的三组数据0123H、4567H和89ABH即为前一周期写入的数据,说明此电路可以正确的读写数据,也可以在一个周期内完成一次读操作和一次写操作。

4 结束语

本文以一款国外公司的DSP为例,介绍了其内嵌的一块DARAM的整体电路,给出了关键部分的具体电路,并结合仿真波形,详细介绍了电路的工作原理,最后采用数模混合仿真的方法,用ADvance MS对整体的电路进行仿真,结果证明此电路可以实现一个周期内的“双存取”功能,可以为DSP乃至SOC中存储器接口电路的设计提供一种参考。

存储器相关文章:存储器原理

脉冲点火器相关文章:脉冲点火器原理

评论