基于DSP Builder的行车道检测的实现

2 基于FPGA的DSP Builder设计流程

Altera DSP Builder将The MathWorks MATLAB和Simulink系统级设计工具的算法开发、仿真和验证功能与VHDL综合、仿真和Altera开发工具整合在一起,实现了这些工具的集成。设计人员可以使用DSP Builder模块迅速生成Simulink系统建模硬件,通过DSP Builder SignalCompiler模块读取由DSP Builder和MegaCore模块构建的Simulink建模文件(.mdl),生成VHDL文件和工具命令语言(Tcl)脚本,进行综合、硬件实施和仿真。

此系统设计首先用MATLAB建立DSP电路模型。电路模型设计完成后,就开始进行系统功能的仿真,这是属于系统级并且基于算法的仿真,与目标器件无关。然后利用置于Simulink电路模型界面的DSP Builder中的Signal Complier将电路模型文件即Simulink模型文件(.mdl)转化为RTL级的VHDL代码表述和Tcl脚本。一旦获得了VHDL描述,就可以在Simulink中调用Quartus II中的综合器生成网表文件。下一步就是调用Quartus II中的编译器,根据网表文件及设置的优化条件进行布线布局和优化设计的适配操作,同时生成用于Moldelsim的时序仿真文件。将最后生成的Programmer Object File(.pof)对目标器件进行编程配置,即可在硬件上形成DSP系统。

3 边缘检测系统的Simulink模型设计

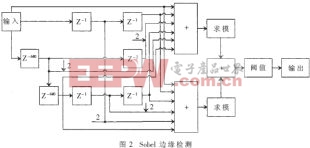

Sobel边缘检测模块包括独立且并行的水平检测和垂直检测两部分。输入缓冲通过一组延时线路转换输入的像素值。线路缓冲器的缓冲级数由图像的宽度决定。本设计采用的图像宽度是640。缓冲器的个数取决于卷积核的大小,本设计采用3×3的Sobel卷积核。垂直和水平方向的边缘检测几乎是相同的,两者之间的区别只在于从输入缓冲器流过的数据流。最后将两部分组合并通过阈值选择形成一幅经过边缘检测的二值图像。Sobel边缘检测是流水线操作,在每一个时钟周期都计算得到一个像素值,如图2所示。图中,Z-640是指本设计输入的图像像素宽度是640,右上角的加法模块实现的是垂直方向的边缘检测,右下角的加法模块实现的是水平方向的边缘检测。对于一般的灰度图像, 其像素的灰度值一般用8位表示,考虑到计算过程中可能出现负数和溢出问题。因此,数据在开始计算前先在最高位补零,使数据宽度变为10 位,计算完成后可再裁剪为8 位。

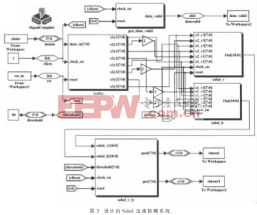

在DSP Builder中设计的Sobel边缘检测系统如图3所示。

4 仿真结果

建立了.mdl文件之后,在Simulink中对其进行系统算法级仿真。设置Matlab各项参数和Simulink仿真参数,因为本设计采用图片的像素是640×480,所以设置仿真时间为307 201s(所有的像素数量加1)。

测试表明,仿真结果符合要求,整个系统算法级设计是正确的。图4为原始的彩色图像,图5为经过水平边缘检测和垂直边缘检测后没有经过阈值选取的图像,图6为经过阈值选取后的二值图像。Sobel算子不像普通梯度算子那样用两个像素的差值,而是采用两列或两行像素灰度加权和的差值来表示,因此有以下两个优点[4]。

(1)由于引入了平均因素,因而对图像中的随机噪声有一定的平滑作用。

(2)由于它是相隔两行或两列之差分,故边缘两侧的元素得到了增强,边缘显得粗而亮。

使用Modelsim进行功能仿真,主要是调用.tcl 文件对RTL 级的VHDL 代码仿真。由于Simulink 的仿真是算法级的,而此仿真是针对硬件结构的,两者之间可能存在软件理解上的差异,所以对RTL 级VHDL 代码的仿真是必要的。仿真结果和系统级仿真一致。编译生成.pof 文件,下载到目标芯片中,从而完成整个边缘检测模块的设计。

参考文献

[1] 贾永红.计算机图像处理与分析[M].武汉:武汉大学出版社,2002.

[2] 李弼程,彭天强,彭波.智能图像处理技术[M].北京:电子工业出版社,2004.

[3] 潘松,黄继业,王国栋.现代DSP技术[M].西安:西安电子科技大学出版社,2003.

[4] 刘禾.数字图像处理及应用[M].北京:中国电力出版社,2005.

评论