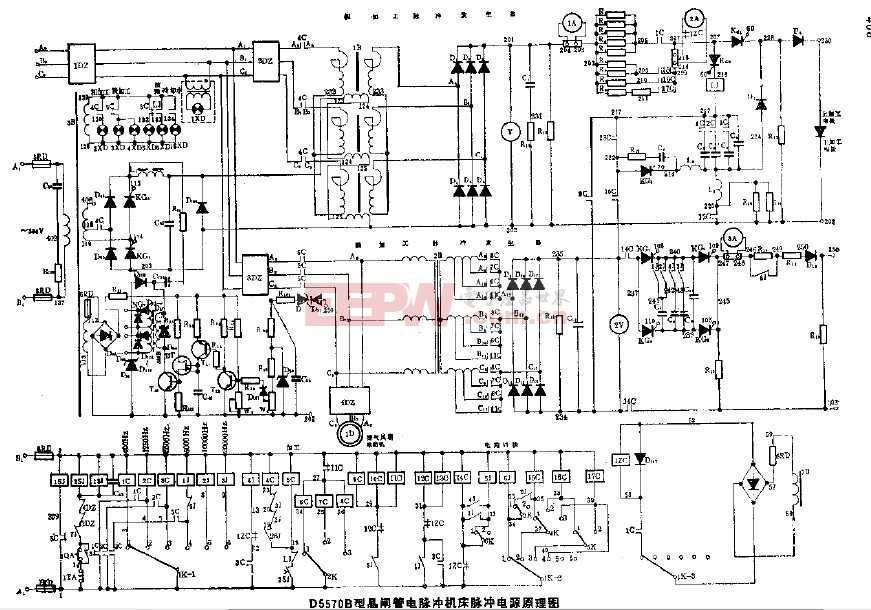

基于FPGA的新型脉冲电源控制系统

原系统的译码器、地址寄存器、数据寄存器、频率合成器、分频器、累加器、地址切换开关、数据切换开关等均集成在FPGA中,取代了用传统TTL器件搭成的复杂系统,简化了PCB设计。

3 FPGA内部功能框图及VHDL设计

在系统中,FPGA要具体实现的功能包括提供正负峰脉冲参考电压,读键盘和A/D的输出以及故障状态,控制系统输出脉冲正负峰的选择,控制输出脉冲数和电源接触器开/关,写A/D控制信号,进行内外触发选择,允许或禁止触发,设定时器初值,控制正常/故障灯亮等。

为此我们采用了模块化设计的思想,按FPGA要实现的功能,将其内部结构分成6个模块,每一个模块对应一个VHDL的设计文件(见图2)。VHDL语言是IEEE标准化的硬件描述语言,其覆盖面广,描述能力强,能支持硬件的设计验证综合和测试。这样设计的好处是有利于各功能模块的编写和调试,提高了软件的可维护性及可读性。

下面给出各个模块的外功能简介:

(1) 信号处理模块SIGNAL-DISPOSAL.VHD

本模块主要接收脉冲开关铁电源的状态信号(电源开/关、控制开/关、触发开/关)、故障信号(热故障、缺相等),以及内部通讯信号(如内部信号输出、允许触发、状态/故障选择等),同时输出控制信号。

(2) 接收数据和发送数据模块RECEIVE-DATA-RXD.VHD 和SEND-DATA-RXD.VHD

这两个模块都有两个输入端口:时钟CLK和复位RESET,分别通过信号RXD和TXD实现与上位机之间的RS232通讯,波特率为9600bps,数据传送格式为11位,依此排序为:起始位(0),数据位(D0、D1、D2、D3、D4、D5、D6、D7),奇偶校验位,停止位(1)。同时与数据处理模块之间分别通过信号允许接收、接收结束、接收错误、接收寄存器 和允许发送、发送结束、发送寄存器联系。当发送结束为0时,发送寄存器送数,允许发送也置为1。

评论