一种实时操作系统RTOS的硬件加速设计

1.1 任务管理和时间管理

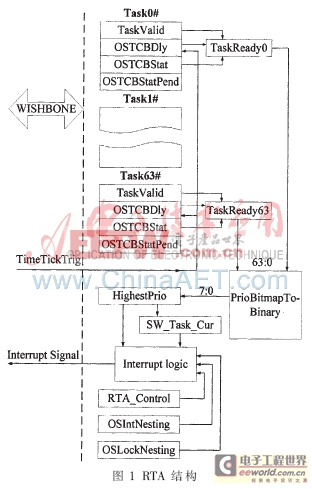

任务管理和时间管理的设计框图如图1所示。

每个任务都有4个域:TaskValid、OSTCBStat、OSTCBDly和OSTCBStatPend。每个任务都有一个任务就绪标志TaskReady,RTA通过PrioBitmapToBinary模块找到最高的优先级并送给HighestPrio。在CPU响应外部中断或者给调度器上锁时,可以通过OSIntNesting和OSLockNesting寄存器关闭RTA的中断。

μC/OS-II实时系统内核中,任务调度基于TimeTick完成,由于程序只能顺序执行,任务的timedly域更新也是顺序执行的,从而使得调度函数的执行时间与运行的任务数量有关。在RTA模块中,基于TimeTick的调度机制并没有改变,只是原型中顺序执行的timedly更新,在硬件中可以同时执行。在使用RTA模块的系统中,移去了软件中的用于任务调度的数据结构,相应地在硬件中予以实现。

当有更高优先级的任务进入就绪态时,就会产生RTA中断。硬件实现上,当进入就绪态的上个时钟周期的最高优先级和本时刻的最高优先级不同时,便产生中断信号。在μC/OS-II中,每个TimeTick时刻都会发生中断,这就需要更频繁地保存CPU寄存器,相比本文提出的方法,浪费了更多的CPU时间。

1.2 TimeTick信号的产生

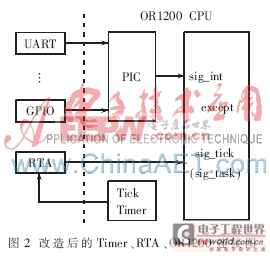

RTA的运行需要一个可配置的Timer来为其产生TimeTick信号。在本文中,通过对OR1200进行改造,利用其内部的Timer产生中断信号作为RTA任务调度的标准时钟节拍,而将RTA的中断信号连接到原来Timer在CPU的接口处。这样,CPU通过Wishbone总线可对Timer进行读写,且RTA产生的中断不会占用可编程中断控制器PIC(Programmable Interrupt Controller)。改造后的框图如图2所示。

评论