基于FPGA的采集卡的图像增强算法应用研究

利用现场可编程门阵列(FPGA)的并行、实时处理的特性,实现图像增强的片上集成系统(SoC)。系统将图2 中的r1 ,r2 ,s1 和s2 设计成接口参数,用户通过主控计算机的应用程序可以反复配置参数,直到得到预期的结果为止。

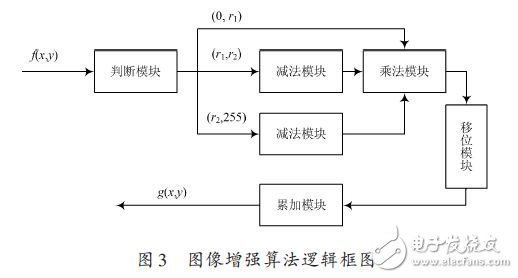

为了方便阐述,把整个FPGA 实现图像增强算法,分为几个阶段。首先,PC 机通过应用程序送r1 ,r2 ,s1和s2 。而后,由驱动程序中的定点化程序将系数进行定点化,后通过PCI9054把式(2)中k1 ,k2 ,k3 ,r1 ,r2 ,s1 ,s2 和移位参数bit1 ,bit2 ,bit3 送到FPGA的内部寄存器中。这样,FPGA中嵌入的图像增强算法模块就能从SDRAM 中取出原始图像数据进行增强,并把经处理后的图像数据存回SDRAM中。图像增强模块首先取回数据,对取回的数据进行判断,把图像数据分为3个区间。并做相应的减法。结果跟定点后的系数进行定点乘法,之后将结果数据进行移位操作,然后通过累加输出结果。常用的并行处理有两种最基本的连接模式:流水线连接和并行阵列连接。针对该算法,采用流水线连接方式进行。在流水线结构中,一个大任务被分解成复杂性大致相同的小任务,各小任务在流水线上同时执行,整个任务的速度取决于执行时间最长的子任务的执行时间。在本论文设计中把增强算法模块化分成判断模块,减法模块,乘法模块,移位模块和累加模块,并将其进行流水连接。算法逻辑框图如图3所示。

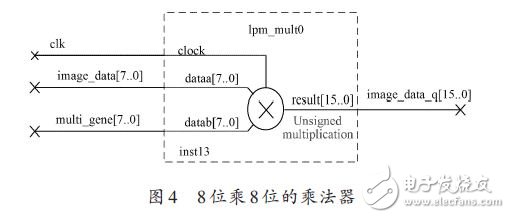

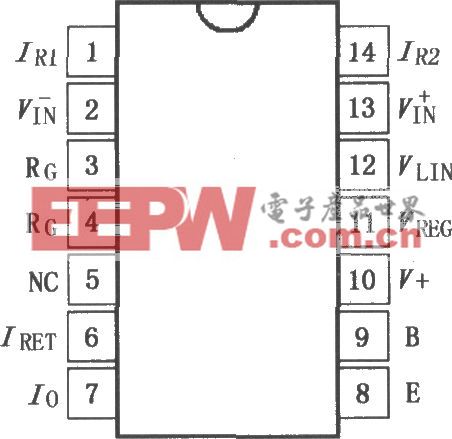

Cyclone器件中的M4K 块支持软乘法器,在设计中采用ALTERA的IP实现。乘法器的IP核如图4所示。

2.2.2 FPGA算法调试结果分析

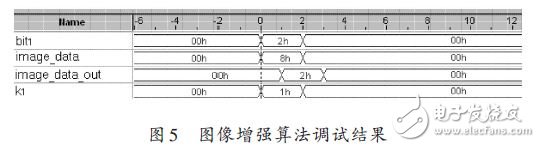

通过SignalTap抓取图像值为0×08的图像增强算法的调试结果见图5.系数k1 为1,bit1 为4时,图像经算法后的像素值image_data_out为1,符合算法结果正确。

3 结论

本文设计开发了一款以FPGA 为核心控制芯片的嵌入式图像采集卡。采集卡以FPGA 为逻辑和算法实现的核心器件,不仅实现了传统意义上的图像采集,而且实现了CCD 相机控制和激光器同步曝光功能,打破了以往单纯靠增加硬件设备实现同步控制的方法,简化了系统硬件结构并节约系统成本。此外,在系统中嵌入了图像增强算法和采用PCI接口与计算机连接满足了高速采集的要求。根据所选芯片的自身特点,设计了相关的图像增强算法。用VHDL和原理图结合的方法对FPGA 进行编程,实现了图像采集系统的各个功能模块。在FPGA内嵌入了图像增强集成系统,用硬件并行处理实现,经仿真该法效果很好。

fpga相关文章:fpga是什么

评论