AI 推动光互连技术应用,实现 GPU 可扩展通信

AI 通常被定义为算力故事:更大的模型、更快的 GPU、布满加速器的数据中心。但随着系统持续扩容,真正的限制并非算力,而是数百、数千乃至数百万处理器间的通信。

图一:人工智能数据中心规模扩展集群规模的演变。

现代 AI 的核心是矩阵乘法,大型神经网络可将运算分配至多个处理单元,并行计算成为提升性能的首选方案。但模型规模超过约 100 亿参数后,小型本地计算域无法支撑扩容,工作负载需分配至多个图形处理器(GPU),覆盖板卡、服务器、机架,乃至跨建筑区域级光纤网络。

实际应用中,GPU 需协同如同一台超大处理器,需在集群内持续交换梯度、参数、激活值与同步流量。该规模下,网络性能与算力深度绑定 —— 数据传输速度不足,加速器将处于等待状态。行业面临 “铜墙瓶颈”,在层级延迟敏感环节形成阻碍,制约扩容集群内 GPU 互联所需的高速链路。

需要明确的是,铜互连并未过时。短距离场景中,电互连成熟、低成本、实用性强。但单通道 200 吉比特每秒信令场景下,权衡劣势凸显:200 吉比特每秒单通道下,直连铜互连传输距离缩短至 1 至 2 米,延长距离需中继器,增加功耗与成本。随着 AI 扩容集群规模更大、密度更高,铜互连已无法满足需求,行业转向光通信,实现更高带宽、更快速度、更高基数与更低功耗。

光互连向内渗透

光通信已在横向扩展网络(机架间、排间链路)成熟应用,当前行业核心议题是未来 AI 系统的光电转换边界。例如,开放计算项目的短距离光互连计划,通过定义光互连需求与指标,提升处理器间、处理器 - 内存带宽。

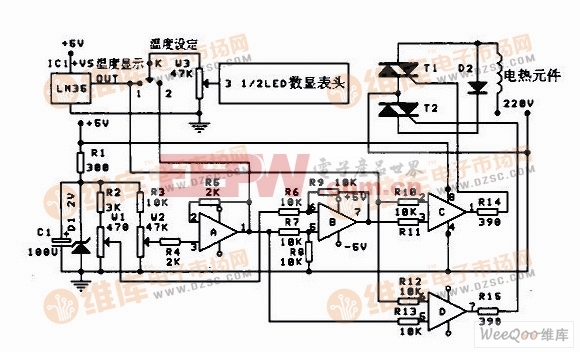

图 2. 人工智能网络中的互连方式。目前,服务器内的 GPU 之间使用铜质互连(2a),而用于服务器之间互连的则是可插拔的光收发器(2b)。未来,带有外部光源的 CPO(光互连处理器)有望用于服务器内部的规模扩展网络(2c)以及服务器之间的规模扩展网络(2d)。

传统插拔式光学设计中,电信号需穿过电路板到达收发器后转换为光信号。在最高数据速率下,这些电气路径的损耗、均衡、功耗与布局复杂度问题愈发突出。共封装光学(CPO)将光引擎直接部署在芯片封装旁,缩短高速铜迹线长度,实现更高带宽密度与更低每比特能耗;传统收发器被拆分为芯片旁光引擎、外部激光源与光纤互连三部分。

行业逐步转向外部激光架构,因激光对温度敏感,与封装最热区域分离更易管控。英伟达与博通均在 2025 年宣布共封装光学重大技术突破,预计 2028 至 2030 年实现量产。

共封装光学:优势显著,挑战重重

共封装光学本质是异质集成难题,需将不同材料体系、器件类型、制造工艺整合至紧凑高性能封装中。行业正探索多种激光方案、调制器方案,以及光引擎、光源、主机专用集成电路(ASIC)的功能划分方式。每种设计选择都会影响封装尺寸、插入损耗、热敏感性、可制造性、成本与长期可靠性。核心挑战不仅是打造高速光链路,更是保障链路可通过封装、认证、量产与现场部署。行业正积极应对这些挑战,2026 年光纤通信博览会(OFC)前后,涌现出多项多源协议,例如光计算互连多源协议、开放共封装多源协议产业联盟。

热管理是最大难题之一。GPU 与交换专用集成电路已处于极高要求的热环境中,将光学器件靠近这些器件,直接引发激光寿命、调制器性能、封装界面与系统稳定性问题。外部激光架构备受青睐的原因之一,是可将温度最敏感的元件远离最热区域,但该选择也带来封装、系统权衡问题,例如对准、布线、可维护性与整体系统复杂度。

制造环节进一步增加难度。光引擎输出光纤数量越多,AI 集群并行性越高、网络拓扑越扁平。但实际应用中,光纤附着是光学组装中最难、成本最高的环节,尤其是需要主动对准的场景。每增加一根光纤,都会影响良率与成本。这意味着最优方案并非物理原理最完美的方案,而是能最佳平衡带宽、组装复杂度、热管理与可制造性的方案。

综上,AI 首先让并行计算成为必需,随后让分布式计算不可避免,如今正推动互连架构重构。光链路已在长距离数据中心网络普及,下一步将深入计算封装内部 —— 铜互连越来越难以满足带宽、传输距离与能效的综合需求。共封装光学成为解决该问题的主流方案,并非因其简单,而是替代方案的扩容难度越来越大。

评论