何时、何地及为何使用芯片组

自几十年前基于VLSI的ASIC兴起以来,单片集成一直是芯片设计的主流方法。在单片设计中,集成电路的所有构件,如逻辑、存储器、模拟接口和专用加速器,都集成在一块硅片上。系统单芯片(SoC)模型为工程师提供了一个紧凑、紧密耦合的架构,并拥有成熟的设计和验证流程。

然而,晶体管的持续扩展和系统复杂度的增加推动了这一方法的极限。现代芯片体积不断扩大,最先进的工艺节点变得更昂贵且对良率敏感。因此,在单一芯片上制造高性能芯片的所有常规功能可能会带来显著的成本、风险和灵活性不足。

在过去十年左右,基于芯片组的架构开始在市场上获得关注。系统不是将所有组件集成到一个大型芯片上,而是被划分为多个较小的芯片组——广义上称为芯片组——每个芯片组针对特定功能进行优化。芯片组单独制造,随后通过先进的互连技术(如2.5D封装和三维叠加)组装成单一封装。

芯片组承诺更高的灵活性、更快的上市时间和降低成本,但它们也带来了新的复杂性。因此,芯片组并非适合所有应用。什么时候转向芯片组设计更合理?在哪些情况下,单体设计是更好的做法?为什么?本文旨在解答这些问题,为工程师提供帮助他们自行决策的见解。

芯片设计师何时、何地及为何采用芯片组

选择芯片组设计的主要因素在于硅面积和成本。

在最先进的芯片中,尤其是数据中心和人工智能(AI)中使用的芯片,单芯片所需的硅片面积可能接近甚至超过现代光刻工具的十字线极限。准星极限由现今300毫米光刻所用光罩面积定义,尺寸为26×33毫米。这意味着单个单片芯片通常不能制造到大约858 mm2。

超过这一阈值,单体整合变得不可行。而且在之前,更大的模具更容易出现缺陷,这会降低良率并推高成本。单个故障可能危及整个芯片,导致巨额成本。

芯片尺寸与采用芯片组最关键的经济原因密切相关:硅的成本。在5纳米或3纳米等先进节点制造大型单片芯片,成本比更成熟节点高出成倍,原因是工艺复杂性和良率降低。高级节点需要更复杂的光刻工艺、额外的工艺步骤和更高的掩膜套装。这些因素增加了基础制造成本——甚至在考虑良率之前。

当硅芯片体积较大时,这些成本因低良率而进一步放大。芯片中含有一个或多个缺陷的概率随着整体硅面积的增加而增加。芯片越大,芯片有很大一部分无法正常工作的风险就越大。不可避免地,这些无效的硅芯片必须被丢弃。

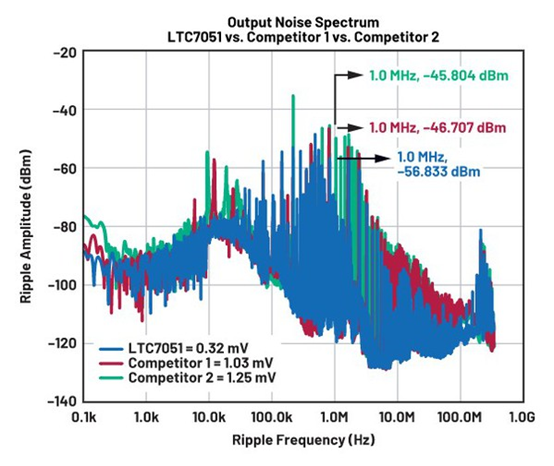

基于芯片组的设计通过将功能分布在更小的芯片上,避免了这一问题,而这些芯片在统计上更有可能无缺陷。最终包装中只有已知良好的模具。实际上,芯片组的良率可超过50%,而大型单片设计中面积相近的产能率可能低于30%(见图1)。

1. 随着芯片面积的增加,基于芯片组的设计始终比单片芯片获得更高的良率(D0 = 缺陷密度)。

另一个重要驱动因素是异构积分。许多复杂系统包含了需求截然不同的功能,例如高速数字逻辑、片上存储器、专用加速器和低功耗模拟接口。这些模块通常在不同的工艺节点上表现最佳或最具成本效益。但在单体设计中,IP的所有构建模块必须在同一基底和工艺上实现,常常导致性能或成本的妥协。

然而,芯片组架构允许每个子系统在最适合该任务的工艺节点上制造,然后在封装层面集成。来自旧设计的经过验证的IP模块,如模拟前端,可以保留原样,而只有关键数字逻辑更新到新节点,从而降低开发时间和风险。

芯片组还在架构层面引入了模块化和可重复使用性。芯片组一旦验证和鉴定,就可以在多种设计中重复使用,而无需重复完整的设计和验证周期。因此,工程师在更新系统功能或升级芯片设计以针对不同性能或功能配置时,可以更快地工作。这种方法也降低了为大型客户打造定制硅片的门槛。

最后,芯片组架构在可扩展性方面具有优势。通过集成额外的芯片组,可以增加新功能,而无需重新设计整个系统。如果设计问题发生在单个模块中,只需重做或重新鉴定该芯片组,从而降低风险并加快开发速度,相较于单体流程中的全芯片重做。

这些优势与行业日益增长的愿景相契合,即开发可现成采购的标准化芯片组,从而加快上市时间、降低开发成本,并打造具竞争力的即插即用组件生态系统。

为什么单片芯片设计仍然是行业标准

尽管芯片组架构日益受到关注,单片ASIC在许多情况下仍被青睐。

主要原因是架构上的简洁性:将所有功能集成到一块芯片上,避免了芯片组分区带来的额外设计、测试和封装复杂性。此外,工程师在设计SoC方面有数十年的经验,他们知道在验证和测试时该关注什么。他们还能使用成熟的电子设计自动化(EDA)工具,有助于降低单片芯片开发的困难。

此外,测试过程更为简单。单体设计受益于既有的为测试设计(DFT)方法,并由现有工具支持。所有功能都集中在一个芯片上,因此无需协调芯片间的测试或考虑互连中潜在的故障模式。这使得系统级验证比基于芯片组的设计更为简洁和可预测。

单片芯片设计还实现了功能模块之间的紧密集成,最大限度地减少了互连延迟并最大化带宽。对于时间限制严格的系统——即紧耦合计算核心之间,或处理器核心与共享内存块之间需要低延迟通信——即使是极小的延迟也会降低性能。在这种情况下,单个骰子上方块的物理接近性仍是关键优势。

此外,基于芯片组的方法带来了系统层面的不确定性,行业仍在不断解决这些问题。挑战包括建立包装技术标准,以及确保在热应力和机械应力下的长期可靠性,这两项领域仍处于活跃发展阶段。

测试也需要创新。虽然芯片组经过严格测试,但放入包装后可能表现不相同。单独访问芯片组进行测试也可能带来困难,尤其是在硅芯片放置在三维堆栈中时。

因此,对于不推动芯片面积限制或不需异构集成的系统,单片设计的简单性可能超过芯片组所提供的模块化和灵活性。

慎选:芯片组带来的工程挑战

虽然单片集成在许多情境下仍是更直接的选择,但芯片组的潜在优势可能因此需要额外的复杂性。但如果决定转向基于芯片组的架构,将面临一系列新的工程挑战。

一个关键考虑因素是划分策略(见图2)。换句话说,哪些功能模块可以在不牺牲延迟、带宽或时序的情况下被隔离?

2. 传统SoC中的逻辑、内存、模拟及其他功能模块被划分为芯片组并重新组装成单一封装,实现异构集成和提高良率。

第一步是评估划分的技术可行性。需要严格时序或高带宽的功能模块,通常难以分离,否则会引入不可接受的延迟。相比之下,交互有限的模块,如模拟与数字逻辑或独立加速器,通常更适合放置在独立芯片上。

另一个重要因素是优化设计中不同工艺节点。例如,模拟电路通常在更成熟的节点上发挥最佳性能,而数字磁芯则受益于先进的晶体管缩放。将这些模块拆分到芯片组中,可以在最能产生影响的地方使用先进工艺技术,而无需将相关成本应用于整个设计。

然而,分区不可避免地增加了测试和验证的复杂性。每个芯片组必须独立验证,并且作为组装系统的一部分进行验证,包括芯片组间连接。设计者可能需要在芯片和封装层面同时插入测试逻辑,并且可能需要为单个芯片单独供电,使得功率传输比单片流更复杂。此外,芯片对芯片互连引入了新的失效模式和验证挑战,这些问题仍在行业内不断探索。

芯片设计师还需要新的软件工具来应对基于芯片组设计的复杂性。虽然芯片组可以像其他单片芯片一样设计,但作为一个整体系统来全面检查整个设计仍然很有挑战性。因此,尽管支持在不断提升,芯片组设计、系统级测试建模标准、互连仿真和热成像等EDA工具的稳定性尚未达到单片设计的水平。

通用芯片互连快递(UCIe)及其他标准旨在简化多芯片集成。但这些标准在实际应用,尤其是在汽车等领域,依然艰难。

在这种情况下,机械可靠性和封装的严格要求常与标准接口假设相冲突。例如,当前规范允许通过基板垂直连接,但由于机械应力和长期耐用性的担忧,这在高可靠性系统中不可行。

这些标准不仅解决物理和协议层面的互作性,还在不断发展以支持系统层级要求,如安全性、保障性和可测试性。

此外,热量和物理限制也会影响芯片组在封装内的布局。功率可以更有效地在芯片组系统中分配,在某些情况下可能简化冷却工作。但要充分利用这一点,还需要精心布置和布线。

例如,热点会降低系统性能。在拥堵区域内路由信号和电力可能导致互联路径变长,这也可能带来影响。同时,物理布局限制,如有限的基底路由资源,可能限制芯片组的定位和连接方式。

芯片组今天最有意义的地方——以及不合适的地方

那么,如何在单芯片集成和芯片组集成之间做出决定?最终,决策取决于应用的具体情况:性能要求、系统复杂性、封装限制、成本敏感性和资格认证要求都会影响最优架构。

在数据中心和高性能计算等领域,使用芯片组已成为越来越多的标准程序。这些系统通常需要较大的芯片面积来容纳计算和内存子系统,这会挑战准星极限,增加当量损失的风险。

芯片组允许计算和内存块分散到多个芯片块上,每个芯片可能构建在不同的节点上,并且更有效地分散热负载。分区还允许在多个系统配置中重复使用经过验证的组件。

芯片组集成在汽车先进驾驶辅助系统(ADAS)和自主计算平台(见图3)中也持续受到关注。这些系统通常需要大型、异构的SoC,且具有严格的可靠性要求。

3. 汽车系统中的芯片组集成支持可扩展性、更快的开发和提升可靠性。

芯片组可以通过隔离关键功能来帮助独立芯片,并允许子系统在最终组装前独立测试。例如,工程师可以在高性能SoC中集成重复的计算芯片组,以相互监控故障,或在其中一个芯片故障时无缝接管。

目前,芯片组在汽车行业中仍然相对罕见,因为像UCIe这样的标准还处于开发初期阶段。它们在机械稳健性、热应力或长期可靠性方面尚未得到广泛验证。

相比之下,其他市场即使在复杂度极高的情况下,仍然偏好整体整合。例如,在金融系统中,延迟是主要关注点。即使是芯片间通信引入的微秒级延迟也存在问题。在该领域,尽管成本较高,大型单片芯片仍是首选架构,因为它们提供稳定的性能并最小化紧耦合功能模块之间的通信延迟。

移动和物联网设备通常也偏好单体集成,因为它们优先考虑最小体积、低功耗和紧密集成的功能。这些要求使得芯片组封装的复杂性变得不合理。

随着封装标准的成熟和系统级鉴定流程的演进,芯片组可能在新领域带来新兴的优势。例如,在航空航天行业,容错通常通过在系统层面使用多个冗余芯片来实现。通过将冗余集成芯片组,可能降低系统复杂度并提高效率,同时保持鲁棒性。

芯片组会成为芯片制造的新标准吗?

归根结底,芯片组是芯片设计工具箱中的另一个工具。从单片芯片设计向多芯片架构的转变,完全是关于在设计限制、应用需求和技术成熟度所塑造的权衡之间取得平衡。

当系统突破芯片尺寸限制、需要异构集成,或受益于模块化和重复使用时,芯片组提供了显著优势。在这种情况下,选择性地使用高级节点并更灵活地迭代的能力,可以抵消分区带来的额外复杂性。

此外,这一转变得到了包装和基底技术进步的支持。介质器材料、凸起间距和布线密度的创新,使得芯片组可以更靠近,从而实现更高的带宽、更低的比特能量和减少寄生效应。

同时,当简洁性、延迟和紧密耦合功能至关重要时,单体集成仍然是首选选择。成熟的设计流程、成熟的工具和可预测的性能继续使单片ASIC成为高效的解决方案,尤其适用于小型、低功耗或延迟关键的应用。

芯片组会在未来五到十年内成为默认集成策略吗?不太可能。芯片组代表一种互补的架构策略,而非所有设计方法的替代品。未来几年,单片式和芯片组方法将继续共存,每种方法均根据所建系统的具体需求进行选择。

评论